在上一篇浪涌抑制電路?中,給出了一個針對柵極-源極電壓中產(chǎn)生的浪涌的抑制電路示例。本文將會通過示例來探討正電壓浪涌的對策和其效果。

正電壓浪涌對策

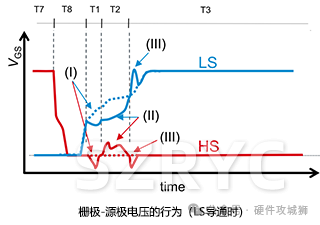

右圖顯示了同步升壓電路中LS導(dǎo)通時柵極-源極電壓的行為,該圖在之前的文章中也使用過。要想抑制事件(II),即HS(非開關(guān)側(cè))的VGS的正浪涌,正如在上一篇文章的表格中所總結(jié)的,采用浪涌抑制電路的米勒鉗位用MOSFET?Q2、或誤導(dǎo)通抑制電容器C1是很有效的方法(參見下面的驗證電路)。

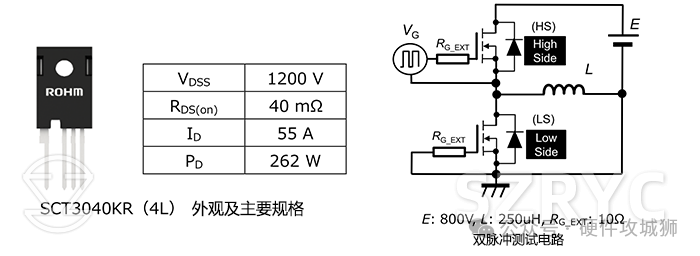

為了驗證抑制電路的效果,將抑制電路單獨安裝在SiC MOSFET(SCT3040KR)的驅(qū)動電路上并觀察了其波形。下面是所用SiC MOSFET的外觀和主要規(guī)格,僅供參考。

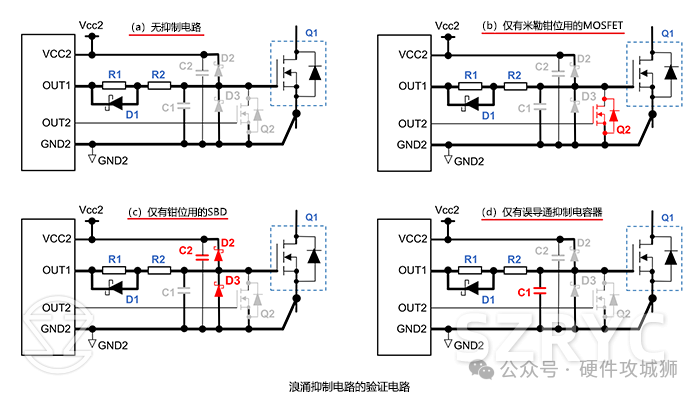

以下電路為用來驗證的抑制電路,共四種:(a)無抑制電路,(b)僅有米勒鉗位用的MOSFET(Q2),(c)僅有鉗位用的肖特基勢壘二極管D2、D3、C2,(d)僅有誤導(dǎo)通抑制電容器C1。通過“雙脈沖測試”確認了GS的浪涌電壓。

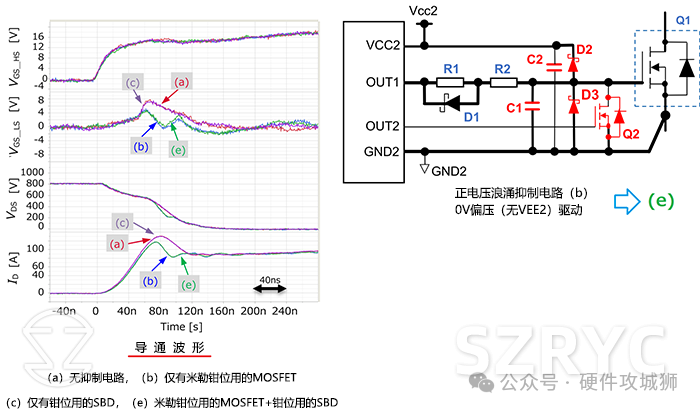

下面是使用了各驗證電路的雙脈沖測試的波形。這是導(dǎo)通時的波形,從上到下依次顯示了開關(guān)側(cè)柵極-源極電壓(VGS_HS)、非開關(guān)側(cè)柵極-源極電壓(VGS_LS)、漏極-源極電壓(VDS)、和漏極電流(ID)。同時,給出了前述的抑制電路(a)、(b)、(c)的波形,并將上一篇文章中的正電壓抑制電路(b)的波形作為“(e)”一并列出。(e)的電路是配備了前述(b)~(d)所有抑制電路的電路。

從上面的波形圖中可以明顯看出,在沒有對策電路的(a)和只有鉗位SBD的(c)中,可以看到結(jié)果是未能抑制正浪涌電壓,VGS_LS波形隆起,并顯著超過了柵極導(dǎo)通閾值,ID也比其他電路大。也就是說,非開關(guān)側(cè)的MOSFET(在本例中為LS)發(fā)生了誤導(dǎo)通。

要想防止這種誤動作,配備有米勒鉗位電路的對策電路 (b) 是必不可少的措施。而實際安裝米勒鉗位電路時,需要能夠驅(qū)動米勒鉗位用MOSFET的控制信號。該信號需要在監(jiān)控VGS電壓的同時控制驅(qū)動時序,一般情況下,很多驅(qū)動IC都具有該功能,但如果使用不具有該控制功能的驅(qū)動IC,則很難實現(xiàn)這種對策電路。

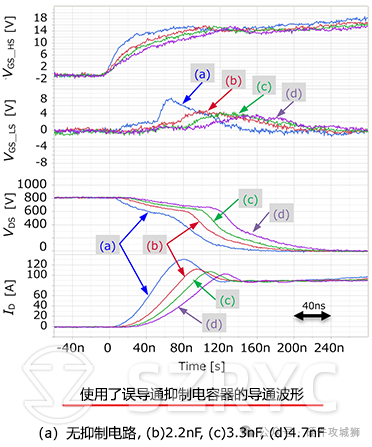

在這種情況下,如驗證電路(d)所示,可以在MOSFET的柵極-源極間連接誤導(dǎo)通抑制電容器C1,作為浪涌對策電路。連接了誤導(dǎo)通抑制電容器C1時的導(dǎo)通波形如下圖所示。波形(a)是沒有C1的波形,波形(b)、(c)和(d)是有C1、C1分別為2.2nF、3.3nF和4.7nF時的波形。從圖中可以看出,與沒有C1的(a)相比,在具有C1的(b)、(c)和(d)中,VGS_LS的波形隆起更小,ID的導(dǎo)通浪涌也更小。

但是,從ID的波形中也可以看出,當連接了誤導(dǎo)通抑制電容器C1時,導(dǎo)通動作會根據(jù)其電容量而減慢,從而會導(dǎo)致開關(guān)損耗增加。因此,C1的容值應(yīng)該選用所需要盡量小的值。在此次的評估中,波形(b)所示的2.2nF可以說是正合適的。