隨著EDA平臺(tái)服務(wù)趨于網(wǎng)絡(luò)化,如何通過(guò)對(duì)資源和流程的有效管理,為用戶提供更為方便安全的遠(yuǎn)程EDA平臺(tái)調(diào)用服務(wù),已成為關(guān)鍵問(wèn)題。在FPGA開(kāi)發(fā)平臺(tái)上集成了EDA工具環(huán)境,并部署SGD軟件。在實(shí)現(xiàn)遠(yuǎn)程控制的基礎(chǔ)上構(gòu)建一個(gè)可兼容異構(gòu)系統(tǒng)的EDA工具遠(yuǎn)程調(diào)用接口,解決了EDA工具的遠(yuǎn)程啟動(dòng)和圖形界面?zhèn)鬏攩?wèn)題,得到一種相對(duì)簡(jiǎn)單方便又有一定安全保障的遠(yuǎn)程控制模式,實(shí)現(xiàn)可視化的在線虛擬集成電路芯片設(shè)計(jì)。

1 引言

當(dāng)前,中國(guó)所采用的FPGA芯片基本依賴于進(jìn)口,研發(fā)具有自主知識(shí)產(chǎn)權(quán)的FPGA芯片具有重要意義。FPGA芯片研發(fā)必須使用EDA工具。EDA(Electronic Design Automation)是在CAD技術(shù)基礎(chǔ)上發(fā)展起來(lái)的計(jì)算機(jī)軟件系統(tǒng),是指以計(jì)算機(jī)為工作平臺(tái),融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理及智能化技術(shù)的最新成果,進(jìn)行集成電路芯片產(chǎn)品的自動(dòng)設(shè)計(jì)。EDA集成開(kāi)發(fā)環(huán)境IDE(Integrated Development Environment)是指根據(jù)集成電路芯片設(shè)計(jì)流程,將設(shè)計(jì)流程中各個(gè)階段所需要的EDA工具軟件集成在一個(gè)硬件平臺(tái)上,進(jìn)行項(xiàng)目設(shè)計(jì)開(kāi)發(fā)的軟硬件工作環(huán)境。在此環(huán)境中,項(xiàng)目的設(shè)計(jì)數(shù)據(jù)通過(guò)文件方式在各個(gè)EDA工具之間流轉(zhuǎn),直到設(shè)計(jì)全過(guò)程結(jié)束。集成電路芯片EDA設(shè)計(jì)工具很多,其中按市場(chǎng)所占份額排主要有Cadence、Mentor Graphics和Synopsys。這三家都是ASIC設(shè)計(jì)領(lǐng)域相當(dāng)有名的軟件供應(yīng)商。集成電路芯片EDA設(shè)計(jì)工具包含了集成電路芯片開(kāi)發(fā)的各個(gè)領(lǐng)域:前端設(shè)計(jì)、后端設(shè)計(jì)和設(shè)計(jì)驗(yàn)證。前端設(shè)計(jì)工具將完成從芯片邏輯部分的概念化設(shè)計(jì)到芯片邏輯門(mén)級(jí)表示的工作。后端設(shè)計(jì)描述了如何使設(shè)計(jì)結(jié)構(gòu)在芯片上物理實(shí)現(xiàn),關(guān)鍵是芯片庫(kù)單元的布局和布線。設(shè)計(jì)驗(yàn)證將保證芯片滿足功能、時(shí)序、功率和其他指標(biāo)的要求。

21世紀(jì)EDA技術(shù)的發(fā)展日新月異。中國(guó)先后在7個(gè)國(guó)家產(chǎn)業(yè)化基地建立了EDA技術(shù)與服務(wù)平臺(tái)。從功能上看,這些EDA平臺(tái)上安裝有當(dāng)前所有主流EDA軟件和測(cè)試工具,并配備有相應(yīng)的設(shè)計(jì)環(huán)境,以租用的方式提供給企業(yè)使用。然而,目前能夠以網(wǎng)絡(luò)平臺(tái)為載體向用戶提供在線IC設(shè)計(jì)的平臺(tái)還很少,僅適用于進(jìn)駐的企業(yè),對(duì)于遠(yuǎn)程訪問(wèn)的企業(yè)則無(wú)能為力。

本文FPGA開(kāi)發(fā)平臺(tái)集成了FPGA芯片設(shè)計(jì)流程中各個(gè)階段所需要的Cadence、Synopsys、Mentor等公司的各種EDA工具,用于研發(fā)具有自主知識(shí)產(chǎn)權(quán)的千萬(wàn)門(mén)級(jí)FPGA課題產(chǎn)品。在自主千萬(wàn)門(mén)級(jí)FPGA芯片設(shè)計(jì)課題中有海外設(shè)計(jì)團(tuán)隊(duì)參與,為了不受地域限制來(lái)使用開(kāi)發(fā)平臺(tái)上的EDA工具,又不影響數(shù)據(jù)安全,使用SGD軟件是目前最佳的方法。SGD(Secure Global Desktop)軟件基于互聯(lián)網(wǎng)的遠(yuǎn)程仿真計(jì)算技術(shù),能夠?qū)崿F(xiàn)可視化的在線虛擬集成電路芯片設(shè)計(jì),用戶通過(guò)網(wǎng)頁(yè)瀏覽器即可使用FPGA開(kāi)發(fā)平臺(tái)上集成的EDA工具和資源。在數(shù)據(jù)安全方面,由于在FPGA開(kāi)發(fā)平臺(tái)服務(wù)器和用戶終端之間傳輸?shù)膬H僅是鼠標(biāo)鍵盤(pán)的輸入和屏幕的變化量,用戶終端只負(fù)責(zé)交互,所有計(jì)算和存儲(chǔ)都在平臺(tái)服務(wù)器端完成,所以能夠保證設(shè)計(jì)數(shù)據(jù)的安全。

2 EDA工具集成和SGD軟件部署總體框架

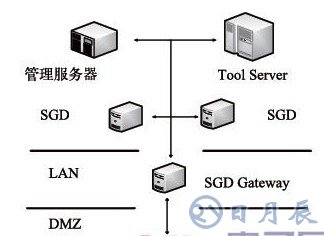

EDA工具集成和SGD軟件部署總體框架如圖1所示。

圖1 EDA工具集成和SGD軟件部署總體框架

服務(wù)器端的功能由SGD Server陣列、SGD Gateway Server、管理服務(wù)器以及多臺(tái)EDA Tool Server共同承擔(dān)。用戶通過(guò)互聯(lián)網(wǎng)與SGD Gateway Server相連。管理服務(wù)器提供用戶認(rèn)證、許可證管理、版本控制和缺陷追蹤等功能。EDA Tool Server用于各類EDA工具的安裝和運(yùn)行。 SGD Server陣列為用戶訪問(wèn)資源和調(diào)用工具提供界面和負(fù)載均衡。SGD Gateway Server提供安全加密訪問(wèn)通道。在此架構(gòu)中,用戶端的運(yùn)行環(huán)境一般為Windows系列,而服務(wù)器端的運(yùn)行環(huán)境包括了Linux、Solaris、Windows Server等多種操作系統(tǒng)。

3 EDA工具集成

3.1 NIS服務(wù)器

網(wǎng)絡(luò)信息服務(wù)(NIS)利用客戶機(jī)/服務(wù)器模式和遠(yuǎn)程過(guò)程調(diào)用(RPC)接口在主機(jī)之間進(jìn)行通訊。網(wǎng)絡(luò)信息服務(wù)由服務(wù)器、客戶機(jī)程序庫(kù)和一些管理工具組成。在FPGA開(kāi)發(fā)平臺(tái)中,用戶一般需要在多臺(tái)Linux機(jī)器上工作,每臺(tái)機(jī)器上用相同的用戶名、屬于相同的組、使用相同的密碼。建立NIS服務(wù)器,將這些需要共享的信息存放在NIS服務(wù)器上統(tǒng)一管理,其他機(jī)器都從NIS服務(wù)器獲得信息,一旦要更改某個(gè)用戶的信息,只需要在NIS服務(wù)器上進(jìn)行更改, 其他機(jī)器就自動(dòng)收到更改后的信息。完成整個(gè)NIS網(wǎng)絡(luò)環(huán)境的建設(shè)之后,就能根據(jù)設(shè)計(jì)項(xiàng)目對(duì)設(shè)計(jì)人員進(jìn)行分組管理,根據(jù)所做項(xiàng)目為其配置相應(yīng)的EDA使用環(huán)境。

3.2 網(wǎng)絡(luò)文件系統(tǒng)(NFS)

網(wǎng)絡(luò)信息服務(wù)通常和網(wǎng)絡(luò)文件系統(tǒng)一起使用。NFS可用于不同類型計(jì)算機(jī)和操作系統(tǒng)之間通過(guò)網(wǎng)絡(luò)進(jìn)行文件遠(yuǎn)程訪問(wèn)和共享。在FPGA開(kāi)發(fā)平臺(tái)中,配置AutoFS Map文件來(lái)集中管理NIS域內(nèi)所有的NFS共享目錄。AutoFS的工作流程是,當(dāng)客戶端配置好AutoFS Map文件,在客戶端如果有NFS目錄讀寫(xiě)請(qǐng)求,系統(tǒng)進(jìn)程automountd就自動(dòng)把NFS服務(wù)器的資源掛接到客戶機(jī)上。所有機(jī)器通過(guò)NFS共用tools目錄,不需要在每臺(tái)機(jī)器上安裝EDA工具軟件,使得整個(gè)EDA設(shè)計(jì)環(huán)境進(jìn)行集中和統(tǒng)一管理。所有機(jī)器通過(guò)NFS共用home目錄,用戶登錄到NIS域中的任一臺(tái)機(jī)器,自己的home目錄內(nèi)容都相同。

3.3 Modules軟件

隨著EDA工具的更新,系統(tǒng)中一定會(huì)存在同一工具的不同版本。版本不同,其路徑、庫(kù)和license等環(huán)境變量都有可能不同,如果用戶在使用中臨時(shí)修改環(huán)境變量會(huì)比較困難。FPGA開(kāi)發(fā)平臺(tái)用Modules軟件進(jìn)行EDA工具的環(huán)境變量管理。modules是一系列腳本的集合,簡(jiǎn)化了shell的初始化,允許用戶在工作過(guò)程中很容易地修改環(huán)境變量,減少其維護(hù)難度,提供了一種動(dòng)態(tài)修改應(yīng)用環(huán)境的機(jī)制。modules使用以下方式工作,$ module avail列出可以加載的工具, $ module load加載工具,$ module list列出已加載的工具,$ module unload卸載工具。在腳本中還可以設(shè)置工具之間的依賴或沖突關(guān)系。

3.4 版本控制和缺陷追蹤軟件

在整個(gè)FPGA開(kāi)發(fā)流程中,每個(gè)設(shè)計(jì)環(huán)節(jié)都需要團(tuán)隊(duì)來(lái)完成。在多團(tuán)隊(duì)緊密合作開(kāi)發(fā)流程中,版本控制和缺陷追蹤等管理軟件是必不可少的。在FPGA開(kāi)發(fā)平臺(tái)上,安裝了SVN、SOS版本管理軟件和bugzilla缺陷追蹤軟件。SVN是開(kāi)源軟件,適合芯片設(shè)計(jì)流程中的文檔版本管理。SOS是ClioSoft公司開(kāi)發(fā)的集成電路設(shè)計(jì)數(shù)據(jù)版本控制軟件,支持Cadence公司virtuoso平臺(tái)的DFII。 開(kāi)源的Bugzilla是一個(gè)搜集缺陷的數(shù)據(jù)庫(kù),它用于記錄和管理產(chǎn)品缺陷從發(fā)現(xiàn)到修復(fù)的全流程。

3.5 EDA工具軟件

根據(jù)EDA工具對(duì)操作系統(tǒng)版本的要求,分別在兩臺(tái)tool server上安裝redhat enterprise 4 update 8和redhat enterprise 5 update 8兩個(gè)版本的操作系統(tǒng)。集成電路芯片設(shè)計(jì)集成環(huán)境需要滿足foundary廠家PDK庫(kù)的要求。PDK(process design kit)是溝通IC設(shè)計(jì)公司、代工廠與EDA廠商的橋梁。PDK用代工廠的語(yǔ)言定義了一套反映foundary工藝的文檔資料,包含了反映制造工藝的基本數(shù)據(jù)集。根據(jù)PDK對(duì)EDA工具及版本的要求,在兩臺(tái)tool server上按照FPGA芯片設(shè)計(jì)流程,集成了設(shè)計(jì)流程中各個(gè)階段所需要的Cadence、Synopsys、Mentor等公司的EDA工具。

4 SGD軟件部署

SGD軟件部署分為兩個(gè)部分,SGD網(wǎng)關(guān)和由多臺(tái)SGD服務(wù)器組成的陣列。SGD網(wǎng)關(guān)是一種代理服務(wù)器,部署在防火墻隔離區(qū)(DMZ)。在客戶端與陣列中的SGD服務(wù)器建立連接之前,通過(guò)SGD網(wǎng)關(guān)先在DMZ中對(duì)所有連接進(jìn)行驗(yàn)證。SGD服務(wù)器陣列和其他需要控制訪問(wèn)權(quán)限的應(yīng)用系統(tǒng)放置SGD網(wǎng)關(guān)后側(cè),位于內(nèi)部網(wǎng)絡(luò)中。SGD服務(wù)器陣列由多臺(tái)SGD服務(wù)器組成一個(gè)負(fù)載均衡和故障轉(zhuǎn)移組,與管理服務(wù)器和tool server連接。

SGD利用遠(yuǎn)程控制技術(shù)構(gòu)建一個(gè)可兼容異構(gòu)系統(tǒng)和工具的中間接口,是一種基于圖形模式的遠(yuǎn)程控制技術(shù),將遠(yuǎn)程主機(jī)桌面和應(yīng)用程序完全地顯示到客戶端,使用戶能夠直觀地對(duì)服務(wù)端進(jìn)行操作。在FPGA開(kāi)發(fā)平臺(tái)中,EDA工具集成環(huán)境中的各種應(yīng)用,如linux系統(tǒng)的EDA工具和windows系統(tǒng)的各種資源等應(yīng)用程序,都可以通過(guò)SGD遠(yuǎn)程顯示,遠(yuǎn)程用戶用IE瀏覽器或Firefox瀏覽器通過(guò)互聯(lián)網(wǎng)就能夠使用FPGA開(kāi)發(fā)平臺(tái)上的各種應(yīng)用軟件。

5 FPGA開(kāi)發(fā)平臺(tái)應(yīng)用

本文介紹的大容量FPGA設(shè)計(jì)平臺(tái)已應(yīng)用于全自主千萬(wàn)門(mén)級(jí)FPGA芯片設(shè)計(jì)。30多位設(shè)計(jì)工程師使用該平臺(tái)參與全自主千萬(wàn)門(mén)級(jí)FPGA芯片設(shè)計(jì)。團(tuán)隊(duì)中在異地工作的工程師使用SGD遠(yuǎn)程登錄到FPGA設(shè)計(jì)平臺(tái)共同參與設(shè)計(jì)工作。設(shè)計(jì)團(tuán)隊(duì)采用中芯國(guó)際SMIC 40 nm CMOS設(shè)計(jì)技術(shù),用正向設(shè)計(jì)的方法,設(shè)計(jì)基于SRAM配置的面向高性能通用邏輯與信號(hào)處理的全自主千萬(wàn)門(mén)級(jí)FPGA器件。器件含有數(shù)字ASCI電路、全定制電路、數(shù)模混合電路以及memory complier等。

6 結(jié)束語(yǔ)

本文介紹了FPGA開(kāi)發(fā)平臺(tái)中EDA工具集成的各種技術(shù),以及部署SGD軟件實(shí)現(xiàn)遠(yuǎn)程訪問(wèn)的方法。FPGA開(kāi)發(fā)平臺(tái)是為面向高性能通用邏輯與信號(hào)處理的自主千萬(wàn)門(mén)級(jí)FPGA課題產(chǎn)品研發(fā)建立的設(shè)計(jì)平臺(tái)。在此平臺(tái)上設(shè)計(jì)團(tuán)隊(duì)不受地域限制,通過(guò)瀏覽器即可遠(yuǎn)程使用平臺(tái)集成的各種EDA工具。在FPGA開(kāi)發(fā)平臺(tái)上,已經(jīng)完成第一個(gè)全自主千萬(wàn)門(mén)級(jí)FPGA的第一次MPW芯片設(shè)計(jì),打通了數(shù)字ASIC設(shè)計(jì)、定制設(shè)計(jì)、數(shù)模混合設(shè)計(jì)全流程。