為提高集成架構中車電總線通信速率,結合綜合化處理系統項目要求,采用雙總線結合的方式,利用CAN總線和FlexRay總線實現功能及搭配上的互補,提出一種基于現場可編程門陣列(FPGA)的總線接口單元設計方案。通過FPGA完成CAN總線控制器、FlexRay總線控制器、RapidIO總線接口等模塊功能,實現高速接口的控制和擴展,并使模塊接口具備可配置能力。測試結果表明,CAN接口及FlexRay接口在指定的波特率下均工作正常,滿足項目要求的各項性能指標。

1 概述

CAN總線是一種有效地支持分布式控制或者實時控制的串行通信網絡,具有多主機、高性能以及高可靠性。然而隨著汽車電子技術的發展,早期的CAN總線已經不能很好地解決眾多電子設備之間的實時通信問題。由FlexRay聯盟制定的FlexRay協議標準成為一種理想的解決方案。FlexRay通訊協議運用于可靠的車內網絡中,是一種具備故障容錯的高速汽車總線系統。作為一種靈活的車載網絡系統,FlexRay具有高速、可靠及安全的特點,它不僅能簡化車載通信系統的架構,而且有助于汽車電子單元獲得更高的穩定性和可靠性。FlexRay在物理上通過2條分開的總線進行通信,每一條的數據速率是10 Mb/s。CAN網絡最高性能極限為1Mb/s,而FlexRay總數據速率可達20Mb/s。FlexRay還能夠提供很多網絡所不具有的可靠性特點,尤其是FlexRay具備的冗余通信能力,通過硬件可實現完全復制網絡配置,并進行進度監測。CAN總線和FlexRay總線兩者在功能及搭配上可實現互補。FPGA在數字電路設計上非常靈活且性能強大,在不改變外圍電路的情況下,可以編寫不同的片內電路邏輯,以實現不同功能或進行功能擴展。

本文提出的車電總線接口單元綜合考慮用戶的具體需求,保留CAN總線作為衛星導航設備接口總線,其余接口總線采用高速的FlexRay總線,既兼容較低速接口的通信速率要求,又滿足高速總線接口的需要,將CAN和FlexRay總線結合在一起,基于FPGA,使成本與效益最大化。

2 車電總線架構

本文綜合化處理系統項目中處理系統采用多處理器結構,板間通信數據量較大。若采用PCI總線進行信號傳輸則由于PCI總線帶寬有限,當數據量較大時容易形成通信瓶頸,且PCI總線不支持點對點傳輸。若選用以太網,則傳輸速率較低,軟件開銷較大,且高帶寬帶來的高成本使它在系統內互連時缺乏吸引力。結合項目采用高速實時總線的具體要求,最終選擇基于VPX架構的RapidIO總線進行通信傳輸。VPX總線采用高速串行總線技術替代VME總線的并行總線技術,支持更高的背板帶寬。其交換式結構使得系統整體性能不再受主控板的控制,提高了系統的整體性能。通過串行RapidIO(SRIO)轉換,完成了RapidIO-CAN、RapidIO-FlexRay協議轉換功能,實現了車電總線與任務總線(RapidIO)的無縫連接,進而滿足了處理系統項目高速、多處理器、實時的通信傳輸要求。

2.1 CAN技術

控制器局部網(ControllerAreaNetwork,CAN)屬于現場總線的范疇,它是一種有效支持分布式控制或實時控制的串行通信網絡。CAN的應用范圍遍及從高速網絡到低成本的多線路網絡。

(1) CAN的分層結構

CAN遵從OSI模型,按照OSI基準模型,CAN結構劃分為2層:數據鏈路層和物理層,如圖1所示。

圖1 CAN分層結構

按照IEEE802.2和802.3標準,數據鏈路層又劃分為邏輯鏈路控制和媒體訪問控制;物理層又劃分為物理信令、物理媒體附屬裝置和媒體相關接口。其中,邏輯鏈路控制子層為數據傳遞和遠程數據請求提供服務;訪問媒體控制子層的功能主要是傳送規則,即控制幀結構、執行仲裁、錯誤檢驗、出錯標定和故障界定。

(2) CAN總線的主要特點

CAN為多主工作方式,網絡上的任意節點在任意時刻都可以主動地向其他節點發送信息,不分主從,方式靈活。其采用非破壞性的總線仲裁技術,可以進行點對點、一點對多點和全域廣播方式傳遞信息,多點同時發送信息時,按優先級順序通信,節省總線沖突仲裁時間,避免網絡癱瘓。報文傳送采用短幀數據結構,傳輸時間短,抗干擾能力強,檢錯效果好。網絡節點在錯誤嚴重的情況下可以自動關閉輸出功能,脫離網絡,實現了標準化、規范化。

2.2 FlexRay技術

(1) FlexRay分層結構

FlexRay的分層結構由物理層、傳輸層、表示層及應用層組成。物理層定義了信號的實際傳輸方式,包括在時域上檢測通信控制器故障的功能;傳輸層是FlexRay協議的核心,它的功能是從表示層獲得節點要發送的信息和把網絡上接收的信息傳送給表示層;表示層完成信息過濾、信息狀態處理以及通道控制器與主機的接口;應用層由應用系統定義。

(2) FlexRay節點結構

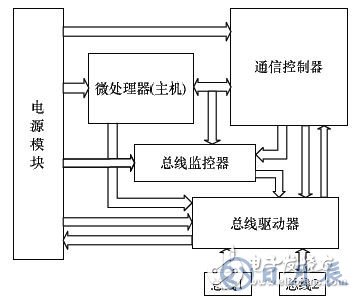

FlexRay節點的核心是ECU(Electronic Control Unit),是接入車載網絡中的獨立完成相應功能的控制單元。主要由電源供給系統、主處理器、固化FlexRay通信控制器、可選的總線監控器和總線驅動器組成。主處理器提供和產生數據,并通過FlexRay通信控制器傳送出去。其中驅動器和監控器的個數對應于通道數,與通信控制器和微處理器相連。總線驅動器連接著通信控制器和總線,或是連接總線監控器和總線。主處理器把FlexRay控制器分配的時間槽通知給總線監視器,然后總線監視器就允許FlexRay控制器在這些時間槽中傳輸數據。數據可以隨時被接收。結構圖如圖2所示。

圖2 FlexRay節點結構

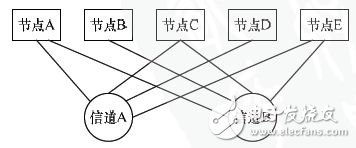

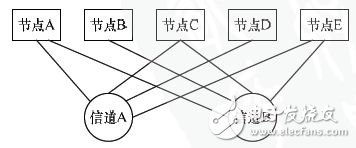

(3) FlexRay網絡拓撲結構

FlexRay的網絡拓撲結構主要分為3種:總線式,星型,總線星型混合型。在星型結構中還存在級聯方式。通常,FlexRay節點可以支持2個信道,在雙信道系統中,不是所有節點都必須與2個信道連接。與總線結構相比,星狀結構的優勢在于:它在接收器和發送器之間提供點到點連接。該優勢在高傳輸速率和長傳輸線路中尤為明顯。另一個重要優勢是錯誤分離功能。雙通道備用星型結構如圖3所示。

圖3 FlexRay網絡拓撲結構

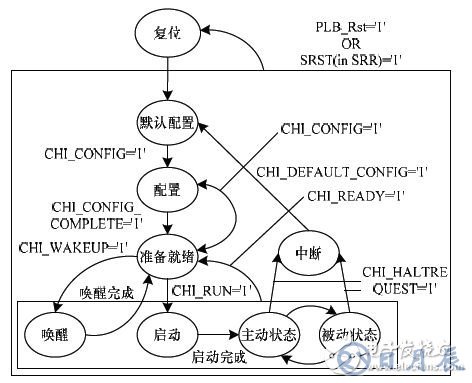

(4) FlexRay狀態

FlexRay的節點有6個基本的運行狀態:

1)配置狀態(默認配置/配置):用于各種初始化設置,包括通信周期和數據速率。

2)就緒狀態:用于進行內部的通信設置。

3)喚醒狀態:用于喚醒沒有在通信的節點。當節點的收發器接受到喚醒特征符后,對主機處理器和通信控制器進行上電,喚醒并激活通信控制器、總線驅動器和總線監控器。

4)啟動狀態:用于啟動時鐘同步,并為通信做準備。只有將節點喚醒后,才能啟動節點工作。系統的啟動由2個邏輯步驟組成,冷啟動節點啟動和其他非冷啟動節點通過接受啟動幀與冷啟動節點整合到一起。

5)正常狀態(主動/被動):可以進行通信的狀態。

6)中斷狀態:表明通信中斷。

FlexRay狀態圖如圖4所示。

圖4 FlexRay狀態

3 車電總線接口單元設計

3.1 總線接口單元組成

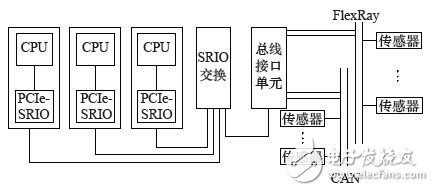

在綜合化處理系統架構中,車電總線訪問可簡化為下列部分:主控單元,RapidIO交換單元,總線接口單元和車電總線。主控單元包含處理器和PCIe-SRIO轉接橋。處理器將信號發送至PCIe-SRIO轉接橋,數據通過SRIO交換,傳輸至總線接口單元,最終實現處理器對車電總線上各傳感器的訪問與控制。車電總線訪問的整體架構如圖5所示。

圖5 系統總體架構

總線接口單元采用3U、VPX結構,板卡主要由XILINX的Virtex6系列FPGA XC6VLX75T完成CAN總線控制器、FlexRay總線控制器、RapidIO總線接口等模塊功能,輔之以CAN和FlexRay總線接口PHY、晶振、電壓轉換器等芯片完成總線接口單元設計。總線接口單元主要完成RapidIO-FlexRay、RapidIO-CAN協議轉換功能,實現了車電總線與任務總線(RapidIO)的無縫連接。由于該總線接口模塊不含FlexRay總線監控功能,若要實現對總線的監控,需在節點上外接監控設備。總線接口單元功能組成框圖如圖6所示。

圖6 總線接口單元功能組成框圖

3.2 車電總線接口設計

3.2.1 CAN總線接口設計

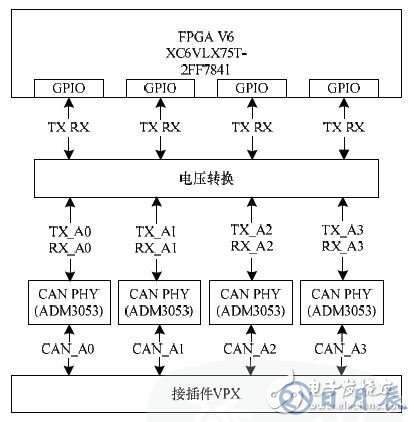

單元模塊通過FPGA輸出四路GPIO信號,GPIO連接電壓轉換芯片以完成電平轉換,CAN總線信號完成電平轉換后連接CAN芯片,從而輸出CAN總線信號與總線接口單元VPX接插件相連,如圖7所示。

圖7 CAN總線接口硬件組成原理

CAN幀時,處理器驅動在內存定義并組織一個下圖結構體,使用RapidIO中NWRITE-R事務,寫入FPGA控制器CAN發送緩沖區地址,即刻完成發送;當CAN控制器完成發送后,將對該處理器產生中斷,告知發送結果。

當接收CAN幀時,處理器驅動在內存定義一個上圖結構體,并將內存地址使用Rapid IO中NWRITE-R事務,寫入FPGA控制器CAN接收緩沖區地址;當CAN控制器接收完一幀后,通過NWRITE-R事務寫入對該處理器地址空間中并產生中斷,告知發送結果。圖8是內存數據結構。

圖8 CAN內存數據結構

3.2.2 FlexRay總線接口設計

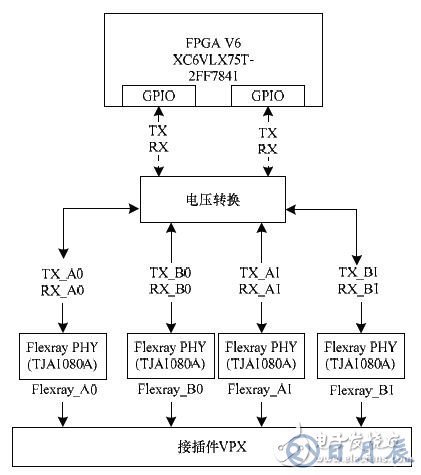

單元模塊通過FPGA輸出兩路GPIO信號,GPIO連接電壓轉換芯片以完成電平轉換,FlexRay總線信號完成電平轉換后各輸出兩路連接FlexRay收發器。由于該XILINX核中只支持FlexRay單信道,因此選擇兩路FlexRay信道形成冗余設計,2組信道都分為A、B2個通道,滿足FlexRay雙信道的要求。收發器選用TJA1080,TJA1080收發器是恩智浦公司出品的一款針對FlexRay的具有高速時間觸發通訊系統的收發芯片,也是全球第一款符合FlexRay協議2.1規定的FlexRay收發器,具有高達10Mb/s的數據傳輸速度。每路信號分別通過JTA1080后,最終輸出四路FlexRay信號,并與總線接口單元VPX接插件相連。詳細結構如圖9所示。

圖9 FlexRay總線接口硬件組成原理

FlexRay每個數據的數據幀由幀頭、有效數據段、幀尾3個部分組成。若為發送,當時間片快到時,鏈表控制器通過RioMaster模塊發送NREAD事務包請求數據,返回的數據進入SendFIFO,由FlexRayIP讀取。若為接收,當時間片到時,鏈表控制器提供接收的基地址,數據收到后將存放于RecvFIFO中,結合接收基地址,通過NWRITE-R寫入遠端內存,之后發送Doorbell使處理器產生中斷。其內存數據結構如圖10所示。

圖10 FlexRay內存數據結構

3.3 FPGA邏輯設計

本文設計通過硬件實現CAN總線控制器、FlexRay總線控制器、RapidIO總線接口等模塊功能。采用Virtex6系列FPGAXC6VLX75T完成RapidIO-FlexRay、RapidIO-CAN協議轉換功能。

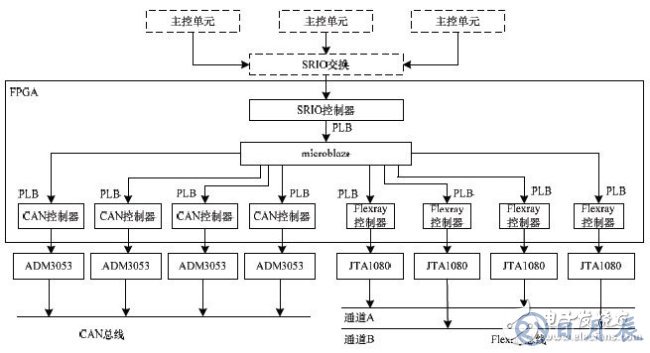

FPGA單元包含SRIO控制器、microblaze軟核及四路CAN控制器和兩路FlexRay控制器。處理器將信號發送至PCIe-SRIO轉接橋,經過橋芯片轉換發送至SRIO交換板。交換板的一端將信號轉發到SRIO控制器上,SRIO核通過PLB總線將控制信號發送至microblaze軟核,經過處理信號通過PLB總線發送至四路CAN控制器和兩路FlexRay控制器。每路CAN控制器均連接CAN轉換器ADM3053,每路FlexRay控制器均連接FlexRay收發器JTA1080。經過轉換器最終分別連接至CAN總線和FlexRay總線上。該邏輯設計的主要特點有3個:

(1)SRIO-PLB橋實現了總線接口單元模塊的srio總線接入功能。

(2)CAN和FlexRay總線控制器通過板載收發器實現了CAN、FlexRay總線的接入功能。

(3)microblaze軟核實現了CAN、FlexRay控制器消息和事件的預處理,完成了與SRIO總線的互連,并做了任務遷移,減輕了主控處理器的壓力。

詳細邏輯結構如圖11所示。

圖11 FPGA模塊內部邏輯結構

4 仿真與驗證

4.1 RapidIO仿真與驗證

在Xilinx的ISE14.1開發環境下,基于車電總線接口單元模塊對RapidIO接口進行了驗證,利用ModelSim對邏輯設計進行仿真,其波形圖如圖12、圖13所示,通過判斷數據的一致性可以驗證RapidIO總線接口的正確性和有效性。

圖12 RapidIO數據發送時序圖

圖13 RapidIO數據接收時序圖

4.2 FlexRay仿真與驗證

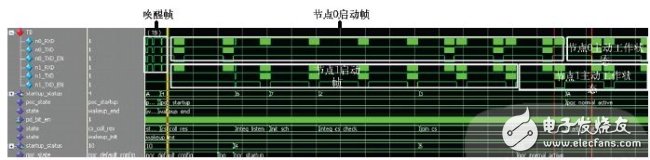

基于車電總線接口單元模塊對FlexRay接口狀態機制進行了驗證,利用ModelSim對邏輯設計進行仿真,其波形圖如圖14所示。

圖14 FlexRay數據收發時序圖

從仿真波形中可以清楚地看出FlexRay狀態機制的變化過程。當節點的收發器接收到喚醒特征符后,對主機處理器和通信控制器進行上電,喚醒并激活通信控制器、總線驅動器和總線監控器。節點0被喚醒后,將返回喚醒完成信號,并處于等待啟動狀態。接著節點1收到喚醒信號,返回喚醒完成信號,節點1進入啟動狀態,節點0也進入啟動狀態,最終都進入主動工作狀態,開始狀態機循環,顯示FlexRay總線接口工作正常。

4.3 CAN仿真與驗證

調用FPGA內的CAN核基于車電總線接口單元模塊對FlexRay接口狀態機制進行驗證,利用ModelSim對邏輯設計進行仿真,結果如圖15所示。端口1發送擴展幀信號,端口0接收,當接收ACK信號時,端口1也接收ACK信號,完成整個擴展幀的收發過程。

圖15 CAN數據收發時序圖

圖15說明了總線接口單元模塊RapidIO接口、FlexRay接口和CAN接口完成仿真測試,工作正常,完成了RapidIO-FlexRay、RapidIO-CAN的協議轉換功能。

5 結束語

目前,筆者所在團隊已成功完成核心處理機系統正樣樣機的整體測試及驗證工作。本文設計在該系統中已經通過功能性測試,基于RapidIO的CAN總線控制器在1Mb/s的最大波特率下工作正常,滿足各項功能指標,基于RapidIO的FlexRay總線控制器在10Mb/s的最大波特率下也滿足各項功能指標。下一步的工作將通過專業的CAN、FlexRay網絡測試儀器對本文設計進行更全面的性能測試,同時將著重解決FlexRay總線接口的信道冗余問題,通過對FlexRay控制器IP核的升級,使之支持雙信道通信,從而滿足FlexRay真正意義上的雙信道冗余要求。