LVDS 是高速、低電壓、低功耗和低噪聲通用 I/O 接口標(biāo)準(zhǔn)。 低電壓擺幅和差分電流模式輸出顯著降低了電磁干擾 (EMI)。 這些輸出有較快的邊沿速率,使信號通路起到了傳輸線的作用。 因此,超高速電路板設(shè)計(jì)和差分信號理論對于設(shè)計(jì)含有 Altera FPGA 并集成了 LVDS 的電路板非常有用。 此外,在設(shè)計(jì) LVDS 電路板時(shí),還需要考慮差分走線、阻抗匹配、交叉串?dāng)_和 EMI 等多種因素。

差分走線

LVDS 采用了差分傳輸機(jī)制,每一 LVDS 信號使用兩條走線。 這兩條走線之間的電壓差定義了 LVDS 信號值。 在對電路板布板時(shí),請按照以下指南進(jìn)行操作,以便在差分走線上成功的傳輸 LVDS 信號。

為盡量減小反射,維持接收器的共模噪聲抑制,差分線在離開驅(qū)動(dòng) IC 后,應(yīng)盡可能彼此靠 近。 而且,為避免差分阻抗出現(xiàn)不連續(xù)點(diǎn),差分 LVDS 信號之間的距離在整條走線上都應(yīng) 保持不變。

為減小偏移,差分 LVDS 走線之間的電信號長度應(yīng)相同。 一路信號在另一路信號之前到達(dá)會(huì) 在信號對之間產(chǎn)生相位差,減小了接收器偏移余量 (RSKM),從而影響系統(tǒng)性能。

減少信號通路上的過孔數(shù)或者其他不連續(xù)點(diǎn)。

電容等任何雜散負(fù)載在差分對的每一條走線上必須大小相同。

為避免信號不連續(xù)性,建議采用 45° 弧線走線而不是 90° 直角轉(zhuǎn)彎。

阻抗匹配

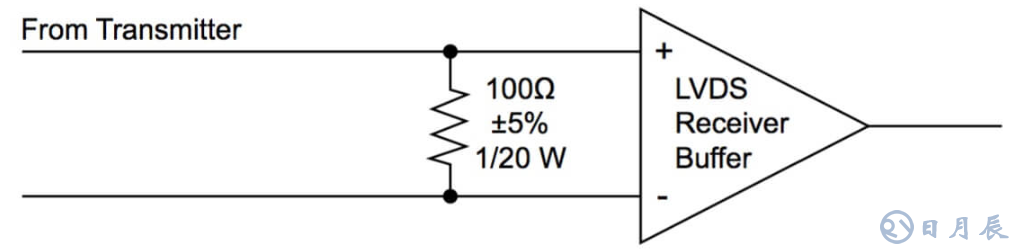

由于是高速 LVDS,因此,阻抗匹配非常重要,即使是非常短的轉(zhuǎn)彎。 差分 LVDS 走線的任何不連續(xù)點(diǎn)都會(huì)導(dǎo)致信號反射,劣化信號質(zhì)量。 這些不連續(xù)點(diǎn)增大了共模噪聲,以 EMI 的形式進(jìn)行輻射。 LVDS 以電流模式輸出,需要匹配電阻實(shí)現(xiàn)閉環(huán),沒有電阻匹配時(shí)無法工作。 所選擇的這一匹配電阻值 (RT) 與傳輸線的差分阻抗相匹配,在 90Ω 到 110Ω 之間 ( 一般為 100Ω)。 圖 1 所示為匹配電阻的正確應(yīng)用。

為 LVDS 通道選擇匹配電阻時(shí),應(yīng)遵從以下指南。

將匹配電阻放在發(fā)射器差分互聯(lián)的遠(yuǎn)端。 可以采用一個(gè) 100Ω 電阻。

采用表面貼薄膜 0603 或者 0805 大小的芯片電阻。

在距離接收器 7 mm 以內(nèi)安裝匹配電阻,盡可能靠近接收器。

LVDS 和單端信號之間的交叉串?dāng)_

為減小 LVTTL、SSTL-3、SSTL-2 以及類似標(biāo)準(zhǔn)等 LVDS 和單端信號之間的交叉串?dāng)_,必須將差分 LVDS 信號與單端信號隔離。 如果 LVDS 和單端信號彼此距離不夠遠(yuǎn),單端信號可能會(huì)給差分對帶來一定的干擾。 靠近單端信號走線的 LVDS 信號受到的影響要比遠(yuǎn)端信號大一些,LVDS 接收器無法將產(chǎn)生的差值信號作為共模噪聲而抑制掉。 雖然干擾不會(huì)導(dǎo)致LVDS接收器錯(cuò)誤的觸發(fā);但是,會(huì)劣化LVDS信號質(zhì)量,從而減小噪聲余量。 在同一 PCB 層上,單端信號距離 LVDS 信號至少 12 mm,以避免交叉串?dāng)_效應(yīng)。 可以采用 VCC 和地平面來隔離 LVDS 信號層和單端信號層。 圖 2 顯示了使用電源平面作為 LVDS 層與單端信號層的屏蔽。

電磁干擾

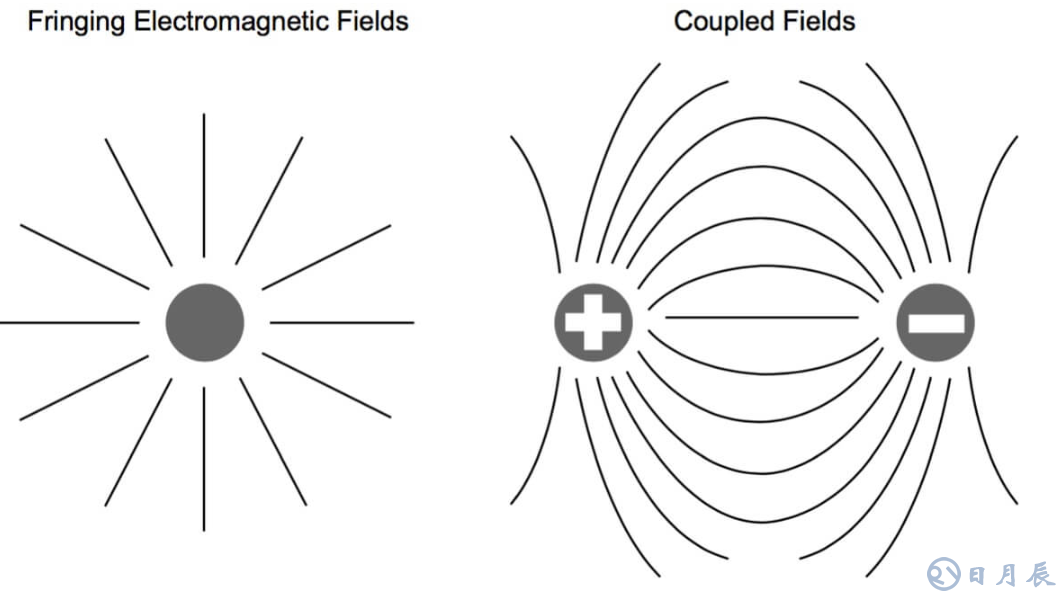

電磁輻射是設(shè)計(jì)人員通常關(guān)心的問題,因?yàn)檩椛鋾?huì)通過電磁橫波 (TEM) 進(jìn)行傳播。 這些電磁波會(huì)穿過屏蔽層,導(dǎo)致系統(tǒng)無法通過電磁兼容性 (EMC) 測試。 采用 CMOS 或者 TTL 等單端傳輸方式時(shí),幾乎所有的磁力線都能夠從導(dǎo)體中自由輻射出去。 一些磁力 線以 TEM 波的形式傳播,從系統(tǒng)中輻射出去,帶來 EMC 問題。

對于 LVDS 差分信號,磁力線彼此抵消,電場相互耦合。 這些電場彼此緊密耦合,無法輻射出去。 只有很少的泄漏場從耦合中輻射出去。 因此,相對于 CMOS 或者 TTL 信號, LVDS 差分傳輸系統(tǒng)的 EMI 要小得多。 圖 3 顯示了單端走線和差分對的電磁場效應(yīng)。

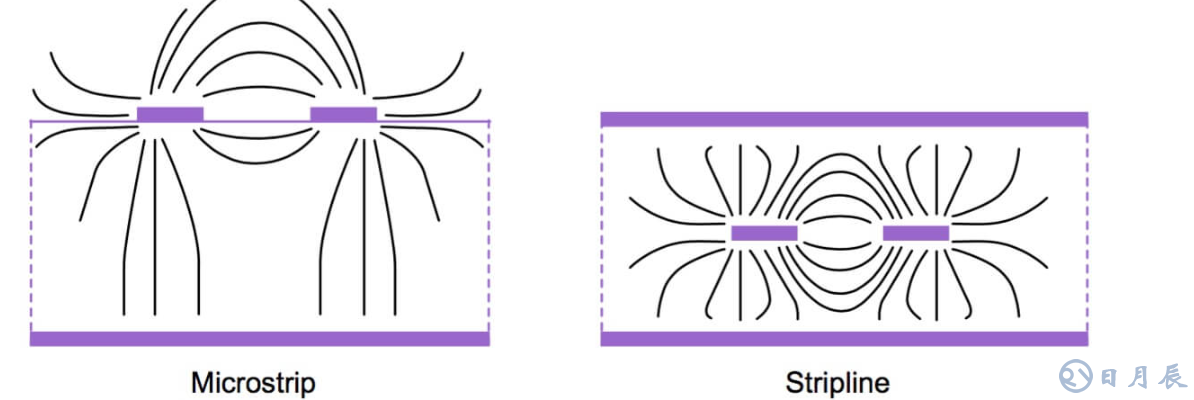

LVDS信號可以布在PCB微帶線(外層)和帶狀線(中間層)之間。圖4顯示了LVDS 帶狀線和微帶線的電磁場輻射。

對于微帶線,下面的地平面耦合了其他的磁力線,從而限制了更多的磁力線,減小了 EMI 的影響。 帶狀線耦合了所有的磁力線,顯著降低了 EMI,但是存在以下不足:

傳播時(shí)間要比微帶線長得多 ( 通常是 1.5 倍 )

需要額外的過孔

需要更多的板層

很難精確的實(shí)現(xiàn) 100Ω 差分阻抗

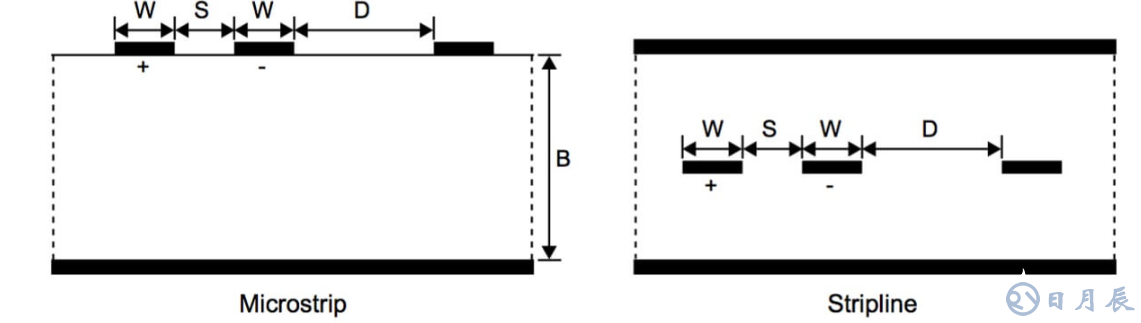

為實(shí)現(xiàn)磁場的最大耦合,差分對兩個(gè)導(dǎo)體之間的間隙應(yīng)盡可能小。 圖 5 顯示了帶狀線和微帶線對的尺寸。

為更好的耦合差分對,S < 2W,S < B,D = 2S,其中:

■ W = 差分對中一條走線的寬度

■ S = 差分對兩條走線之間的距離

■ D = 臨近差分對之間的距離

■ B = 電路板厚度

應(yīng)遵從以下規(guī)則,以實(shí)現(xiàn)差分對兩個(gè)導(dǎo)體之間良好的耦合:

■ 導(dǎo)體之間的距離不應(yīng)超過寬度的兩倍 (S<2W) ■ 電路板的厚度應(yīng)大于導(dǎo)體之間的距離 (B>S)

■ 兩個(gè)臨近差分對之間的距離應(yīng)大于或者等于兩個(gè)獨(dú)立導(dǎo)體之間距離的兩倍 (D>2S)。

通用 PCB 指南

這一節(jié)介紹通用 PCB 布局和供電電壓指南。

常用的FR-4材料適用于低頻(500至600 MHz)應(yīng)用。 高速設(shè)計(jì)可以考慮G-TEK或者聚 四氟乙烯材料。

在設(shè)計(jì)早期階段,沒有進(jìn)行大量的預(yù)布板仿真之前,開發(fā)高效的 PCB 去耦合策略需 要估算去耦合電容數(shù)量、取值和類型。Altera 的電源分配網(wǎng)絡(luò) (PDN) 工具提供這 些關(guān)鍵信息。

使用 LVDS 器件時(shí),應(yīng)采用并聯(lián)的 0.1、0.01 和 0.001 μF 云母、陶瓷或者聚苯乙烯 0805 大小的表面貼芯片電容旁路所有 VCC_CKLK 和 VCC_CKOUT 引腳。 這些電容 應(yīng)在引腳下面,盡可能貼近引腳放置。 除了這些電容,還應(yīng)靠近引腳放置另一個(gè) 2.7 μF 電容。

盡可能靠近連接器放置 LVDS 驅(qū)動(dòng)器和接收器。

發(fā)射器輸出和連接器之間每一條走線的物理長度彼此相差不應(yīng)超過 5 mm,以減小數(shù)據(jù)偏移。

隔離 LVDS 信號和 TTL 信號,以減小交叉串?dāng)_ ( 適用于差分層 )。

分開 LVDS 地和供電平面。

應(yīng)使用寬帶示波器的高阻抗、低電容示波器探針。

保持信號線分支盡可能短。

應(yīng)采用多個(gè)過孔來連接電源和地平面。

LVDS電纜

采用電纜在電路板之間傳送 LVDS 信號。 但是,由于特殊的阻抗匹配和低偏移要求,一般的電纜不一定適用于 LVDS。 按照下面的指南為 LVDS 應(yīng)用選擇電纜:

■ 電纜必須符合 LVDS 的 “匹配阻抗”要求。

■ 電纜的偏移應(yīng)非常小。

■ 導(dǎo)體對必須平衡 ( 例如,兩個(gè)導(dǎo)體穿過電纜后應(yīng)有相同的延時(shí) )。

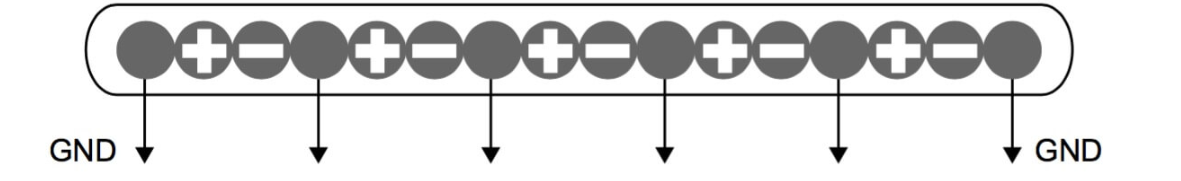

對于低速和距離非常短的傳輸,應(yīng)采用帶狀電纜。 對于距離較長的傳輸和高速應(yīng)用, 使用雙絞線 ( 平衡雙絞線適用于這種情況 )。 如果您使用帶狀電纜,必須由地線將信號對分開,帶狀電纜的邊沿連接器不能用于承載信號。 顯示了用于 LVDS 應(yīng)用的帶狀電 纜。

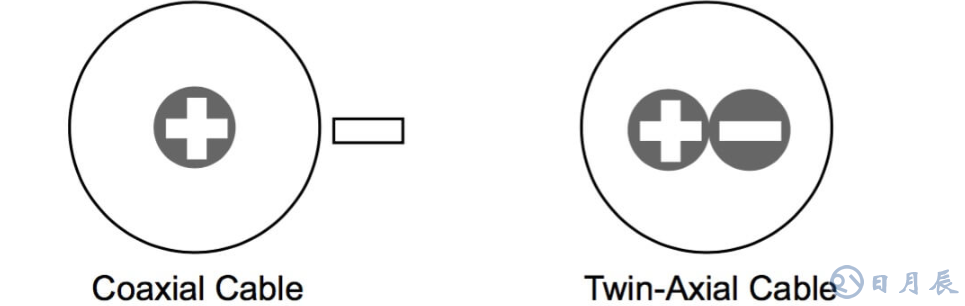

雙軸電纜也可以用于 LVDS,其平衡性能要比同軸電纜好得多。 與同軸電纜相比,由于 場相消效應(yīng),雙軸電纜的 EMI 很小。 圖 7 顯示了雙軸和同軸電纜。

為優(yōu)化性能,使用雙絞線,這是因?yàn)?LVDS 接收器能夠抑制這些電纜帶來的共模電磁輻射。 對于較小的傳輸距離 ( 大約 0.5 m),可以采用 CAT3 平衡雙絞線。 距離大于 0.5 m 時(shí),數(shù)據(jù)速率在 500 MHz 以上的應(yīng)用,使用 CAT5 平衡電纜。

LVDS 連接器

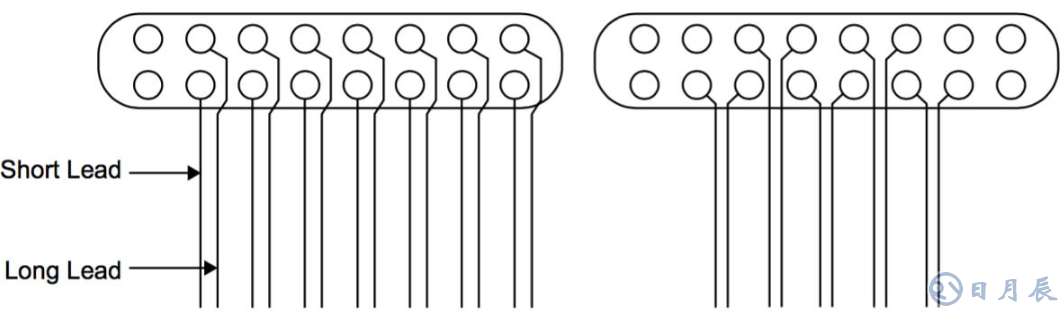

使用連接器連接電路板之間的 LVDS 信號。 圖 8 顯示了 LVDS 連接器較好和較差的例子。 在右面的例子中,差分對長度相同;在左面的例子中,同一差分對的信號有不同的長度,導(dǎo)致出現(xiàn)偏移。

為 LVDS 應(yīng)用選擇連接器時(shí),請按照下面的指南進(jìn)行操作。

連接器應(yīng)具有較小的偏移,阻抗匹配。

應(yīng)選擇導(dǎo)線長度相同的連接器以降低偏移和交叉串?dāng)_。

在連接器上,同一差分對的兩條線應(yīng)彼此靠近放置。

應(yīng)在差分對之間放置地引腳。

連接器的終端引腳應(yīng)可靠的接地,不能用于傳輸高速信號。

連接器所有未使用的引腳都應(yīng)很好的進(jìn)行匹配。

總結(jié)

為充分發(fā)揮高速低噪聲 LVDS 的優(yōu)勢,設(shè)計(jì)人員應(yīng)確保板上和穿過連接器或者電纜的差分走線導(dǎo)體彼此緊密耦合,從而降低噪聲,很好的進(jìn)行平衡,減小偏移,實(shí)現(xiàn)阻抗匹配。、