噴氣織機(jī)的引緯控制系統(tǒng)直接決定著噴氣織機(jī)的運(yùn)行效率、能耗、產(chǎn)品質(zhì)量、平均無故障時(shí)間等關(guān)鍵性的指標(biāo),是噴氣織機(jī)整個(gè)電控系統(tǒng)的核心之一。市場(chǎng)上現(xiàn)存的噴氣織機(jī)的引緯控制系統(tǒng)一般都是利用處理器和硬件電路兩部分配合實(shí)現(xiàn)[2],即引緯角度信號(hào)由處理器通過軟件比較產(chǎn)生,單穩(wěn)態(tài)信號(hào)產(chǎn)生部分和電磁閥驅(qū)動(dòng)部分則由電子元器件組成的硬件電路實(shí)現(xiàn)。

這種控制系統(tǒng)歸納起來主要有以下3個(gè)缺點(diǎn):(1)引緯信號(hào)是通過比較織機(jī)編碼器的角度和預(yù)先設(shè)定的引緯打開關(guān)閉角度產(chǎn)生的。由于CPU的程序是順序執(zhí)行的,在比較這兩個(gè)角度的過程中不可避免地存在不一致性,導(dǎo)致引緯的精度不高,引緯不穩(wěn)定。(2)為了保證引緯電磁閥能夠可靠打開,一般采用48 V電壓打開電磁閥,并且要求信號(hào)持續(xù)時(shí)間為精確的8 ms。傳統(tǒng)的方法是采用單穩(wěn)態(tài)電路產(chǎn)生8 ms的信號(hào),但是單穩(wěn)態(tài)電路容易受到電阻電容精度和溫度的影響,導(dǎo)致定時(shí)精度不高。(3)織機(jī)引緯電磁閥的電路多達(dá)幾十路,需要幾十個(gè)單穩(wěn)態(tài)電路才能滿足要求,電路復(fù)雜,可靠性差,價(jià)格昂貴。

1、引緯控制系統(tǒng)方案設(shè)計(jì)

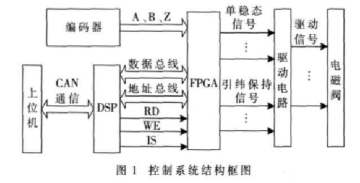

本文所提出的噴氣織機(jī)新型引緯控制系統(tǒng)結(jié)構(gòu)圖如圖1所示。采用DSP控制單元與上位機(jī)進(jìn)行串行通信、與FPGA進(jìn)行并行通信,以實(shí)現(xiàn)引緯參數(shù)的實(shí)時(shí)調(diào)整;FPGA可編程邏輯單元通過比較編碼器的角度信號(hào)和設(shè)定角度信號(hào)產(chǎn)生引緯單穩(wěn)態(tài)和保持信號(hào);引緯單穩(wěn)態(tài)和保持信號(hào)通過驅(qū)動(dòng)電路控制電磁閥的動(dòng)作。

2、引緯控制系統(tǒng)硬件設(shè)計(jì)

引緯控制系統(tǒng)的硬件主要由DSP控制及通信模塊、FPGA信號(hào)產(chǎn)生模塊和驅(qū)動(dòng)電路模塊三部分組成。

2.1 DSP控制及通信模塊

DSP選用TI公司的TMS320LF2407A,它是TI公司專為工業(yè)控制設(shè)計(jì)的一款DSP,具有兩個(gè)事件管理模塊、SPI通信、SCI通信、CAN通信、AD轉(zhuǎn)換等集成外設(shè),其中事件管理模塊包含PWM輸出、比較、捕捉、正交編碼輸入等功能,可以完成除引緯之外的送經(jīng)電機(jī)及卷取電機(jī)的控制、信號(hào)的監(jiān)測(cè)、動(dòng)作的控制等噴氣織機(jī)的其他控制功能。與上位機(jī)通信的硬件電路采用DSP內(nèi)部集成的CAN控制器和外部CAN收發(fā)器PCA82C250。

2.2 FPGA信號(hào)產(chǎn)生模塊

FPGA選用ALTER公司的EP1C6Q240C8,它具有4 KB的內(nèi)部RAM、近6 000個(gè)LE、2個(gè)PLL鎖相環(huán)和185個(gè)I/O口,并具有差分輸入功能,可以滿足本控制系統(tǒng)的性能要求。FPGA模塊主要完成織機(jī)角度信號(hào)的檢測(cè)計(jì)算、并行通信、引緯信號(hào)的產(chǎn)生、信號(hào)的多路選擇、高低壓驅(qū)動(dòng)信號(hào)產(chǎn)生等功能。

2.3 驅(qū)動(dòng)電路模塊

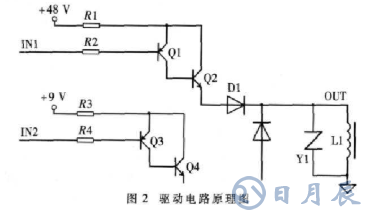

驅(qū)動(dòng)電路采用雙電壓方式,其原理圖如圖2所示。輸入信號(hào)IN1是8 ms的單穩(wěn)態(tài)信號(hào),控制48 V電源打開電磁閥;輸入信號(hào)IN2是引緯的保持信號(hào),控制9 V的電源以保持電磁閥的打開狀態(tài);為了保證足夠的驅(qū)動(dòng)能力,兩路信號(hào)的驅(qū)動(dòng)三極管都采用達(dá)林頓方式;雙二極管D1是為了防止電源切換時(shí)48 V電源串接到9 V電源中;L1為引緯電磁閥,由于電磁閥為感性器件,在電磁閥關(guān)斷時(shí)OUT端因電感的儲(chǔ)能特性會(huì)出現(xiàn)一個(gè)比較高的負(fù)壓,若產(chǎn)生的負(fù)壓高于Q2和Q4三極管的最大承受電壓,則可能會(huì)損壞Q2和Q4三極管。這里的亞敏電阻Y1就是消減過高負(fù)壓的保護(hù)元件。

3、引緯控制系統(tǒng)軟件設(shè)計(jì)

3.1 DSP控制及通信模塊軟件設(shè)計(jì)

在該模塊中DSP采用CAN通信與上位機(jī)傳遞數(shù)據(jù):DSP接收上位機(jī)設(shè)定的打開關(guān)閉角度、慢引緯指令、閥試驗(yàn)指令等數(shù)據(jù),并向上位機(jī)發(fā)送織機(jī)引緯狀態(tài)、織機(jī)角度等顯示信息。

為了更靈活地進(jìn)行數(shù)據(jù)交換,DSP與FPGA以并行數(shù)據(jù)讀寫方式進(jìn)行通信:DSP利用I/O地址空間的高位地址總線的邏輯組合來產(chǎn)生FPGA片選信號(hào),低位地址總線產(chǎn)生要訪問數(shù)據(jù)的地址;利用16 bit數(shù)據(jù)總線傳輸數(shù)據(jù)。在完成串并行通信的同時(shí),DSP通過I/O口把織機(jī)的當(dāng)前狀態(tài)、當(dāng)前花色等信號(hào)輸出給FPGA,保證FPGA中多路選擇器正常工作。

3.2 FPGA信號(hào)產(chǎn)生模塊軟件設(shè)計(jì)

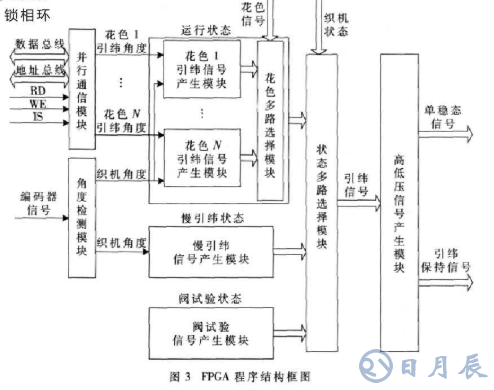

FPGA程序結(jié)構(gòu)框圖如圖3所示,其子模塊有:織機(jī)角度檢測(cè)模塊、并行通信接口模塊、引緯信號(hào)產(chǎn)生模塊、多路選擇模塊、高低壓驅(qū)動(dòng)信號(hào)產(chǎn)生模塊等。

3.2.1 織機(jī)角度檢測(cè)模塊

噴氣織機(jī)的主機(jī)編碼器一般都是相對(duì)型編碼器,其產(chǎn)生角度的A、B、Z三個(gè)差分信號(hào)接FPGA的差分I/O口。Z相是零度信號(hào),當(dāng)Z相輸出有效信號(hào)時(shí),主機(jī)角度為0°;A相和B相輸出相位相差90°的正交信號(hào),當(dāng)A相超前B相90°時(shí)為正轉(zhuǎn),當(dāng)A相滯后B相90°時(shí)為反轉(zhuǎn)。A相和B相邏輯與之后的脈沖數(shù)為織機(jī)轉(zhuǎn)過的度數(shù);每通過一個(gè)脈沖,正轉(zhuǎn)時(shí)主機(jī)角度加一,反轉(zhuǎn)時(shí)主機(jī)角度減一。在FPGA內(nèi)部做一個(gè)計(jì)數(shù)器,Z相信號(hào)為計(jì)數(shù)器的清零信號(hào);A相和B相邏輯與之后的信號(hào)為計(jì)數(shù)信號(hào);A相和B相的相位差為計(jì)數(shù)方向;計(jì)數(shù)器的輸出就是織機(jī)角度,這樣就把相對(duì)型編碼器的信號(hào)轉(zhuǎn)化為0°~360°的織機(jī)角度。

3.2.2 并行通信接口模塊

在FPGA的并行通信接口模塊中,當(dāng)DSP寫數(shù)據(jù)到 FPGA中時(shí),F(xiàn)PGA在DSP的WE信號(hào)的上升沿鎖存數(shù)據(jù)總線上的數(shù)據(jù);當(dāng)DSP讀取FPGA中數(shù)據(jù)時(shí),F(xiàn)PGA在DSP的RD信號(hào)的下降沿把數(shù)據(jù)傳輸?shù)綌?shù)據(jù)總線,保證了DSP可以可靠地寫入或讀取FPGA的數(shù)據(jù)。

3.2.3 引緯信號(hào)產(chǎn)生模塊

噴氣織機(jī)的引緯系統(tǒng)主要工作在運(yùn)行、慢引緯和閥試驗(yàn)三種狀態(tài)。

慢引緯狀態(tài)是噴氣織機(jī)在慢速運(yùn)轉(zhuǎn)時(shí)的單根引緯狀態(tài);閥試驗(yàn)狀態(tài)是為了檢測(cè)電磁閥和引緯電路的好壞而設(shè)置的狀態(tài);運(yùn)行狀態(tài)是噴氣織機(jī)正常工作時(shí)的狀態(tài)。在運(yùn)行狀態(tài),F(xiàn)PGA控制引緯電磁閥按照預(yù)先設(shè)定的引緯角度依次打開和關(guān)閉,形成氣流引導(dǎo)緯紗的運(yùn)動(dòng)。引緯效果的好壞直接關(guān)系到噴氣織機(jī)的整機(jī)性能,也直接決定著布面的質(zhì)量和開車效率。現(xiàn)以運(yùn)行狀態(tài)為例介紹引緯信號(hào)的產(chǎn)生過程。

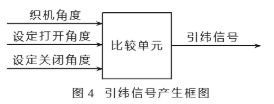

引緯信號(hào)由比較單元比較織機(jī)角度和設(shè)定打開角度、設(shè)定關(guān)閉角度而產(chǎn)生,引緯信號(hào)產(chǎn)生框圖如圖4所示。當(dāng)引緯信號(hào)沒有跨越零度時(shí),即設(shè)定關(guān)閉角度大于設(shè)定打開角度時(shí),引緯信號(hào)在織機(jī)角度大于設(shè)定打開角度且小于設(shè)定關(guān)閉角度時(shí)有效;反之,當(dāng)引緯信號(hào)跨越零度時(shí),即設(shè)定關(guān)閉角度小于設(shè)定打開角度時(shí),引緯信號(hào)在織機(jī)角度大于設(shè)定打開角度或小于設(shè)定關(guān)閉角度時(shí)有效。

噴氣織機(jī)引緯信號(hào)多達(dá)幾十路(根據(jù)花色和幅寬的不同而不同),并且引緯信號(hào)對(duì)控制精度和控制的一致性要求非常高,一般引緯信號(hào)的控制誤差要求不超過1°,在織機(jī)速度為1 200 r/min的情況下,織機(jī)角度1°對(duì)應(yīng)為130 ms左右。

市場(chǎng)上現(xiàn)有的噴氣織機(jī)都是由DSP、單片機(jī)等處理器產(chǎn)生的。由于處理器的程序是順序執(zhí)行的,如果控制誤差不超過1°,就必須在織機(jī)旋轉(zhuǎn)1°的時(shí)間內(nèi)計(jì)算完成幾十路的引緯信號(hào)。也就是說在130 ms內(nèi)完成主程序的一個(gè)循環(huán),這種速度對(duì)于一般的處理器是很難實(shí)現(xiàn)的,特別是在主程序還要完成數(shù)據(jù)的讀取、角度的計(jì)算、通信等功能的情況下,對(duì)于更高速的織機(jī)更是無法實(shí)現(xiàn)。因此市場(chǎng)上現(xiàn)有的噴氣織機(jī)速度一般都不會(huì)超過1 000 r/min,引緯性能也受限于控制的精度、速度和一致性。

FPGA本質(zhì)上是由硬件組成的,其編程語(yǔ)言也為VHDL等硬件描述語(yǔ)言,它的程序并行執(zhí)行,也就是說一旦主機(jī)角度或設(shè)定的打開關(guān)閉角度有變化,幾十路的引緯信號(hào)就會(huì)立即同時(shí)輸出,誤差僅為信號(hào)的建立時(shí)間,只有幾納秒。因此FPGA產(chǎn)生的引緯信號(hào)可以很好地滿足噴氣織機(jī)對(duì)引緯控制精度和控制一致性的要求,從根本上改變處理器產(chǎn)生引緯信號(hào)的弊端。引緯信號(hào)仿真圖如圖5所示:設(shè)定打開角度為80°,設(shè)定關(guān)閉角度為96°,引緯信號(hào)在這個(gè)區(qū)間內(nèi)有效。由圖5可以看出,引緯信號(hào)的產(chǎn)生和關(guān)閉幾乎沒有任何延時(shí)。

3.2.4 多路選擇模塊

由于紡織工藝的要求,不同花色的引緯參數(shù)和引緯系統(tǒng)的不同狀態(tài)需要不同的引緯控制信號(hào)控制電磁閥,在FPGA中可以采用多路選擇器的方式來選擇需要的引緯信號(hào),并且由于是硬件選擇,基本上不會(huì)產(chǎn)生任何誤差和延時(shí)。

3.2.5 高低壓驅(qū)動(dòng)信號(hào)產(chǎn)生模塊

為了保證引緯的可靠穩(wěn)定,電磁閥一般采用雙電壓供電方式,即48 V電壓打開電磁閥,9 V的電壓保持電磁閥的打開狀態(tài)。根據(jù)高速電磁閥性能的要求,控制48 V電壓的信號(hào)要求為精確的8 ms,時(shí)間太短,電磁閥不能可靠打開,時(shí)間太長(zhǎng)電磁閥容易發(fā)熱損壞。

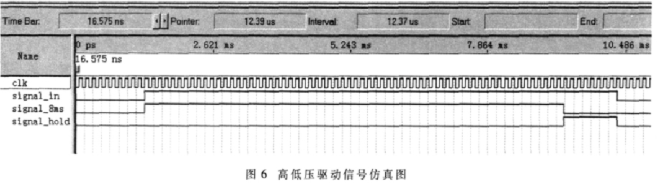

在FPGA中雖然沒有單穩(wěn)態(tài)電路,但是可以采用時(shí)鐘計(jì)數(shù)的方式來模擬單穩(wěn)態(tài)的產(chǎn)生:在信號(hào)的上升沿開始計(jì)數(shù)并設(shè)置單穩(wěn)態(tài)信號(hào)有效,計(jì)滿8 ms的時(shí)鐘脈沖個(gè)數(shù)后停止計(jì)數(shù)并設(shè)置單穩(wěn)態(tài)信號(hào)無效,這樣就可以輸出精確的8 ms單穩(wěn)態(tài)信號(hào)。例如,假設(shè)采用8 k的計(jì)數(shù)時(shí)鐘頻率,64個(gè)計(jì)數(shù)時(shí)鐘周期就是8 ms,單穩(wěn)態(tài)信號(hào)的誤差不會(huì)超過0.125 ms,高低壓驅(qū)動(dòng)信號(hào)仿真圖如圖6所示,其中signal_8ms為8 ms單穩(wěn)態(tài)驅(qū)動(dòng)信號(hào),signal_hold為低壓驅(qū)動(dòng)信號(hào)。

在這種方式中,計(jì)數(shù)時(shí)鐘頻率越高,誤差就越小,大大提高了單穩(wěn)態(tài)信號(hào)控制精度和一致性,完全可以滿足引緯電磁閥的要求。高低壓驅(qū)動(dòng)信號(hào)完全在FPGA中實(shí)現(xiàn),不需要任何附加的硬件電路,不受溫度和電阻電容精度的影響,保證了引緯的可靠性、穩(wěn)定性和控制的一致性,同時(shí)也簡(jiǎn)化電路,減少了硬件故障,降低了成本。

本文提出的引緯控制系統(tǒng)采用FPGA產(chǎn)生引緯信號(hào),達(dá)到了處理器控制中無法實(shí)現(xiàn)的控制速度和控制精度,具有精度高、一致性好、誤差小、穩(wěn)定性好、電路簡(jiǎn)單可靠等優(yōu)點(diǎn)。同時(shí)利用DSP與上位機(jī)及DSP與FPGA之間的通信,可以實(shí)時(shí)調(diào)整引緯參數(shù),實(shí)現(xiàn)控制的靈活性。實(shí)踐和應(yīng)用情況說明,本引緯控制系統(tǒng)完全克服了高速噴氣織機(jī)在引緯控制精度方面的障礙,對(duì)高速織機(jī)的發(fā)展具有重要的意義。