在簡單的了解MOS管的基本原理以及相關參數(shù)后,如何在實際的電路中運用是我們努力的方向。比如在實際的MOS驅動電路設計中,如何去根據(jù)需求搭建電路,計算參數(shù),根據(jù)特性完善電路,根據(jù)實際需求留余量等等,在這些約束條件下搭建一個相對完善的電路。參考了一些資料后,就我目前的需求和自身的理解力分享相關的一些筆記和理解。

1. 常見的MOSFET驅動方式

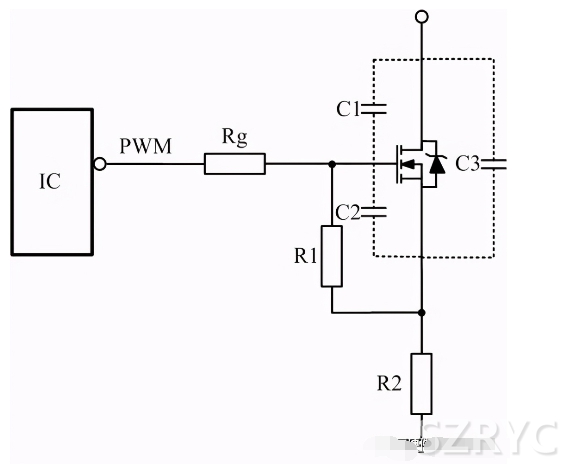

直接驅動

最簡單的驅動方式,比如用單片機輸出PWM信號來驅動較小的MOS。使用這種驅動方式,應注意幾點;一是實際PWM和MOS的走線距離必定導致寄生電感引起震蕩噪聲,二是芯片的驅動峰值電流,因為不同芯片對外驅動能力不一樣。三是MOS的寄生電容Cgs、Cgd如果比較大,導通就需要大的能量,沒有足夠的峰值電流,導通的速度就會比較慢。

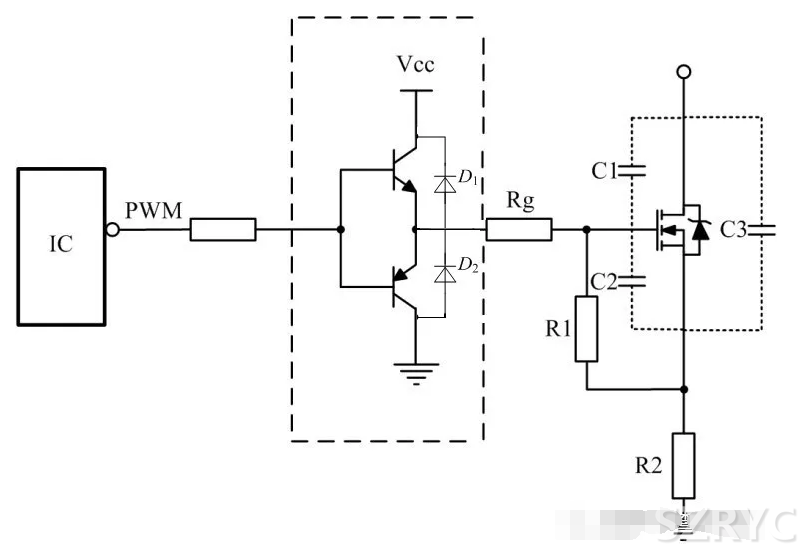

圖騰柱/推拉式驅動電路

由兩個三極管構成,上管是NPN型,下管是PNP型三極管,兩對管共射聯(lián)接處為輸出端,結構類似于乙類推挽功率放大器。利用這種拓撲放大驅動信號,增強電流能力。(驅動IC內部也是集成了類似的結構)

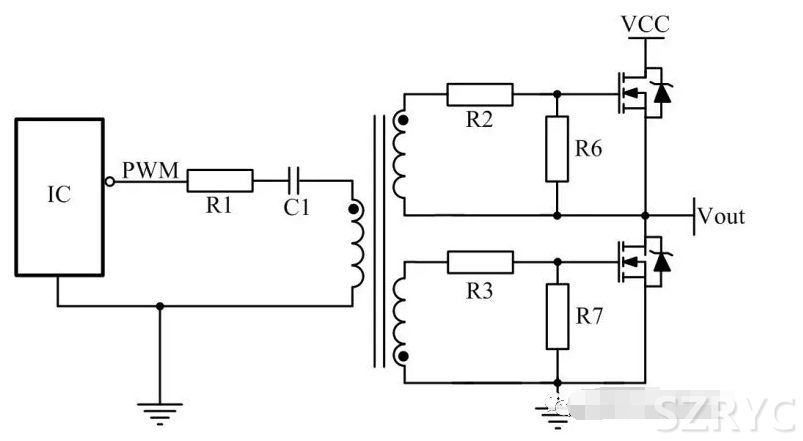

隔離式驅動電路

為了滿足安全隔離也會用變壓器驅動。如圖其中R1抑制振蕩,C1隔直流通交流同時防止磁芯飽和。隔離式的驅動電路不太常見,就不做過多的了解。

小結:當然除以上驅動電路之外,還有很多其它形式的驅動電路。對于各種各樣的驅動電路并沒有一種是最好的,只能結合具體應用,選擇最合適的拓撲。

2. 驅動電路的參數(shù)計算

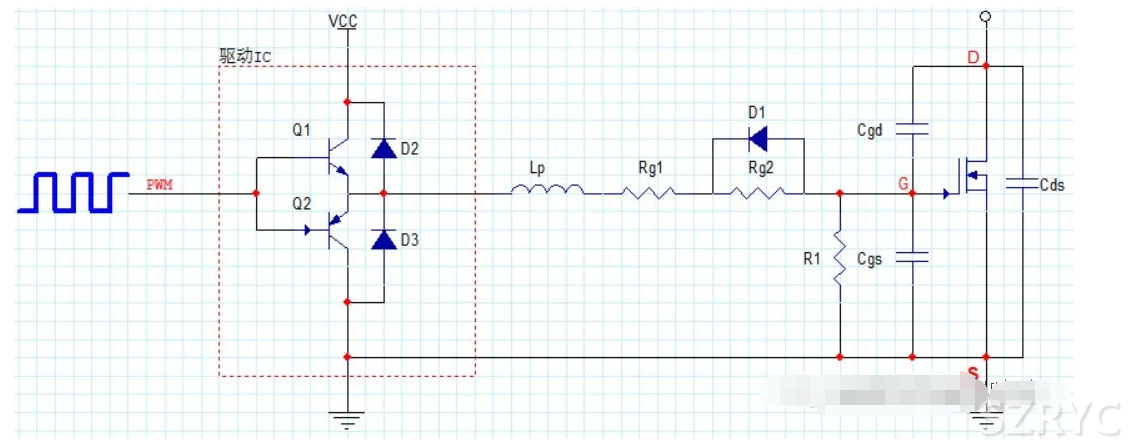

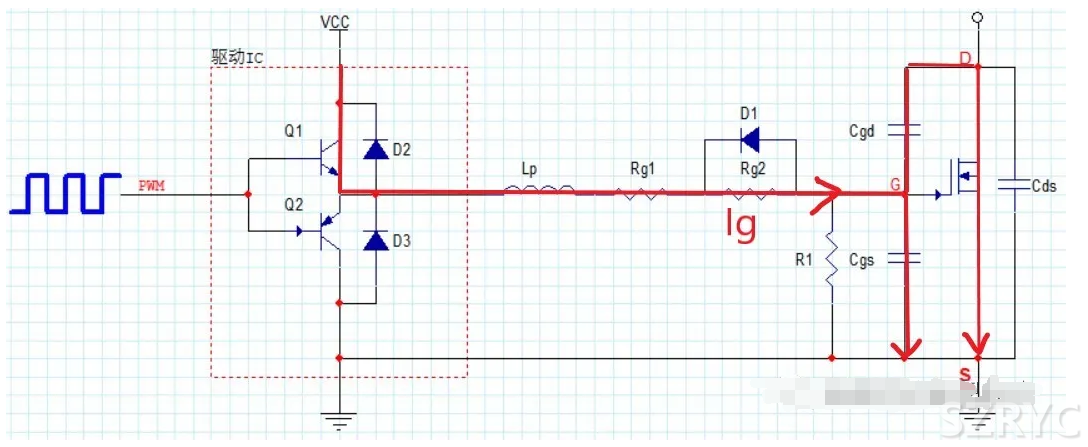

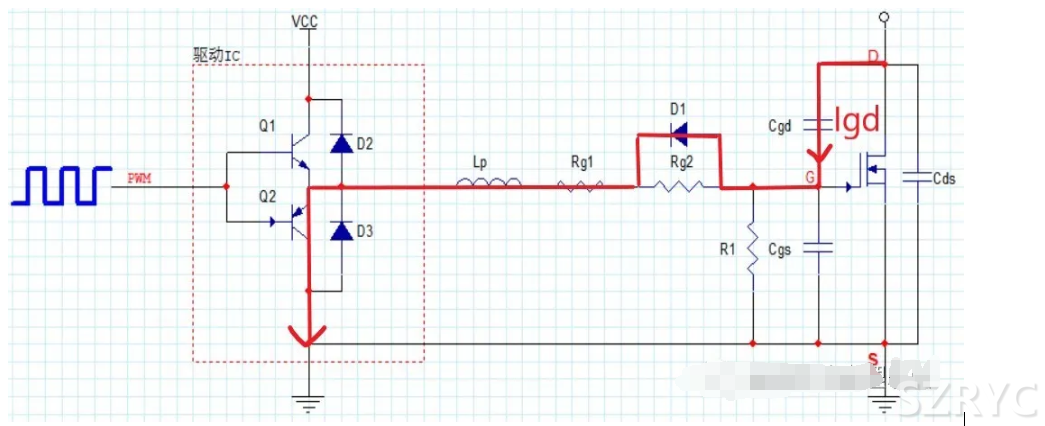

我的實際工作中碰到最多的驅動電路是以下這種能夠控制開關速度的驅動電路,我就以它舉例做進一步的分析。

如圖,在驅動電阻Rg2上并聯(lián)一個二極管。其中D1常用快恢復二極管,使關斷時間減小同時減小關斷損耗,Rg1可以限制關斷電流,R1為mos管柵源極的下拉電阻,給mos管柵極積累的電荷提供泄放回路。(根據(jù)MOSFET柵極高輸入阻抗的特性,一點點靜電或者干擾都可能導致MOS管誤導通,所以R1也起降低輸入阻抗作用,一般取值在10k~幾十k)

Lp為驅動走線的雜散寄生電感,包括驅動IC引腳、MOS引腳、PCB走線的感抗,精確的數(shù)值很難確定,通常取幾十nH。

驅動電阻Rg的計算

驅動走線的寄生電感和MOS管的結電容會組成一個LC振蕩電路,如果驅動芯片的輸出端直接到柵極的話,在PWM波的上升下降沿會產(chǎn)生很大的震蕩,導致MOS管急劇發(fā)熱甚至爆炸,一般的解決方法是在柵極串聯(lián)電阻,降低LC振蕩電路的Q值,使震蕩迅速衰減掉。

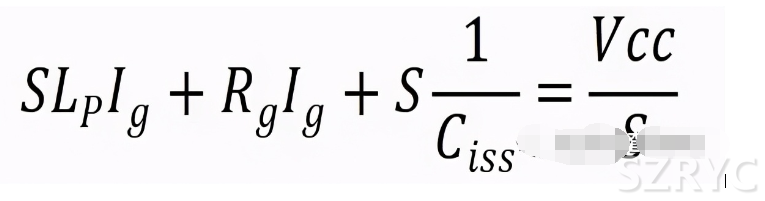

驅動電阻下限值:當mos開通瞬間,Vcc通過驅動電阻給Ciss=Cgs+Cgd充電,如上圖所示(忽略下拉電阻R1的影響)。根據(jù)LC震蕩電路模型,可以列出回路在復頻域內對應的方程。

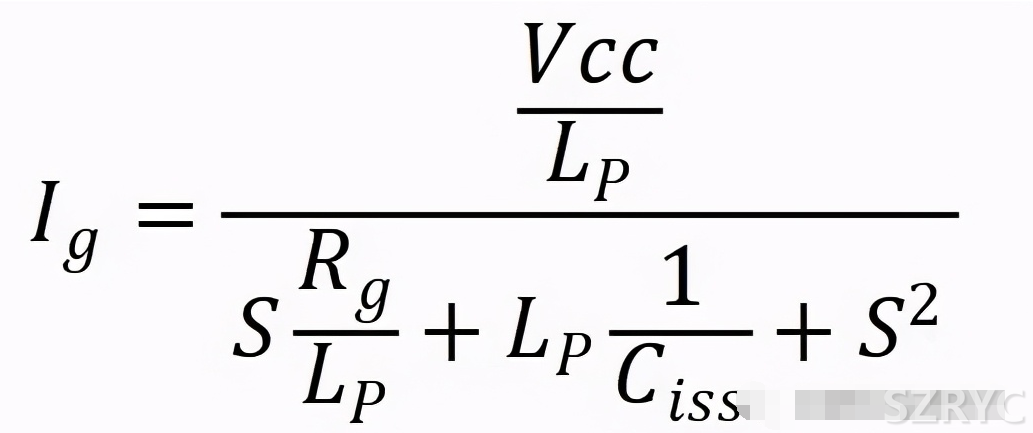

求解出ig,并化為典型二階系統(tǒng)的形式

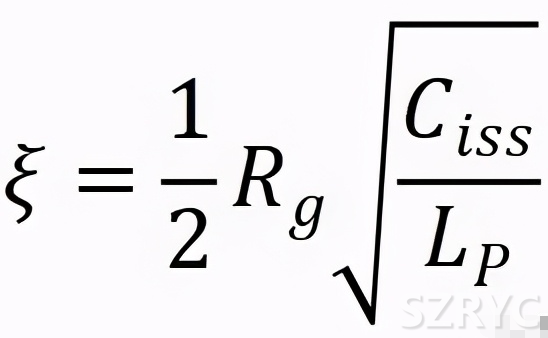

再根據(jù)LC振蕩電路求解二階系統(tǒng)阻尼系比

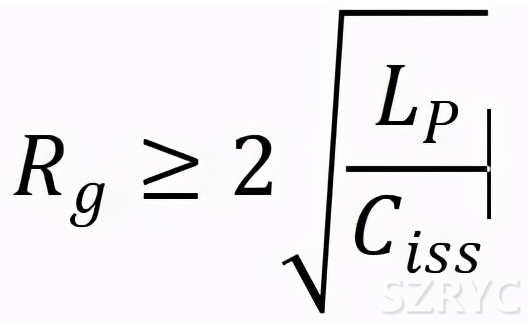

那么根據(jù)LC振蕩電路的特性,為了保證驅動電流ig不發(fā)生震蕩,該系統(tǒng)要處于過阻尼的狀態(tài);即阻尼比必須大于1,則方程式解得Rg=Rg1+Rg2的下限范圍

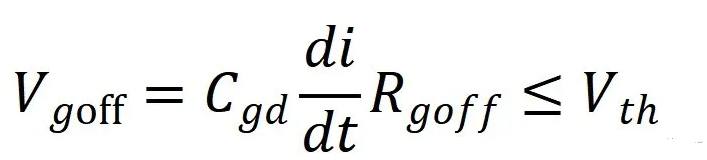

驅動關斷電阻上限值:MOS關斷時,Vds會產(chǎn)生很大的dv/dt,那么由于寄生電容Cgd的存在,就會對回路進行放電繼而產(chǎn)生較大的電流,根據(jù)公式:Ic=Cdv/dt。那么回路上Igd流過驅動電阻Rg,又會在GS間產(chǎn)生一個電壓Vgoff=IgdxRg。這樣我們的方向就是不能讓其高于MOS導通的門檻電壓Vth以避免誤導通。

那么列出不等式

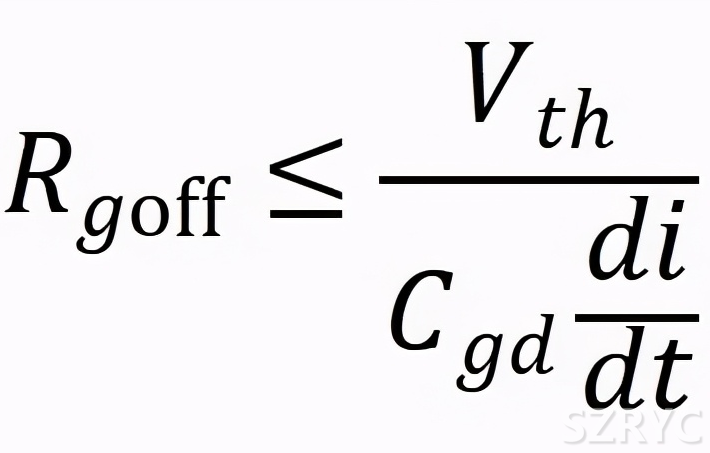

則解得驅動電阻Rgoff=Rg1的取值范圍

總結:

在實際設計中,我們就可以根據(jù)理論公式,以避免驅動電流不發(fā)生震蕩為條件計算出Rg1+Rg2的下限范圍,以避免關斷誤導通為條件得出驅動上限值即得到Rg1的取值范圍。

然后再根據(jù)實際的實驗在考慮損耗、EMI、以及應用在橋式拓撲中的死區(qū)控制等優(yōu)化方向上,不斷調試出想要特性參數(shù)。那么,通過基本的分析后,我們也得出一個MOS驅動電路設計的大方向;一個好的MOSFET驅動電路應當有以下幾點要求:

(1) 導通時,驅動電路應能提供足夠大的充電電流使MOSFET柵源極間電壓迅速上升到所需值,保證開關管能快速開通且不存在上升沿的高頻振蕩。

(2) 開關導通期間驅動電路能保證MOSFET柵源極間電壓保持穩(wěn)定且可靠導通。

(3) 關斷瞬間驅動電路要提供一個盡可能低阻抗的通路供MOSFET柵源極間電容電壓的快速泄放,保證開關管能快速關斷,同時可以提供負壓以避免干擾和誤導通。

(4) 驅動電路結構簡單可靠、損耗小,還要根據(jù)情況隔離。