彈載信息處理系統(tǒng)是一種實時嵌入式數(shù)字處理系統(tǒng),用于對彈載導(dǎo)引系統(tǒng)接收信號進行分析處理,實現(xiàn)對目標信號的檢測、截獲和跟蹤以及目標信息的提取,是彈載雷達導(dǎo)引系統(tǒng)的關(guān)鍵組成部分。隨著軍事技術(shù)的發(fā)展,未來空戰(zhàn)面臨著越來越嚴酷的戰(zhàn)場環(huán)境,對于彈載雷達導(dǎo)引系統(tǒng)的探測能力以及反隱身、抗干擾等性能提出了更高的要求。為此需要采用復(fù)雜處理算法,如數(shù)字波束形成、空時自適應(yīng)處理技術(shù)、雜波抑制、低信噪比信號檢測和識別、超分辨等,提高系統(tǒng)目標探測和抗干擾能力。數(shù)據(jù)處理復(fù)雜度越來越大、實時性要求越來越高,同時彈載應(yīng)用環(huán)境對系統(tǒng)功耗、尺寸又有著嚴格的限制,因此需要運算速度更快、容量更大、功耗更低的數(shù)字處理平臺來實現(xiàn)這些功能需求。基于單核DSP的信號處理實現(xiàn)方式難以適應(yīng)大運算量實時處理的新需求,傳統(tǒng)的DSP互聯(lián)技術(shù)是將多個單核DSP用高速接口連接在一起,但是這樣的系統(tǒng)架構(gòu)會帶來功耗和尺寸方面的問題。采用基于單片異構(gòu)多核處理器的信號處理平臺成為發(fā)展趨勢,以實現(xiàn)高速實時并行處理平臺的小型化、低功耗設(shè)計,顯著提高彈載信息處理系統(tǒng)的信號與信息處理能力。

1 多核處理器TMS320C6678性能

單核DSP其性能通常由時鐘頻率來評價,然而DSP的時鐘頻率并不能做到直線上升,單片單核結(jié)構(gòu)受限于速度極限,很難再有更大發(fā)展空間;隨著應(yīng)用系統(tǒng)復(fù)雜性持續(xù)增加,只通過提高時鐘頻率來增強處理性能達到了極限。單片多核的結(jié)構(gòu)將成為DSP發(fā)展的主流,應(yīng)用單片多核處理器,將顯著提升彈載雷達信息處理系統(tǒng)性能,并能實現(xiàn)彈載雷達信息處理平臺更進一步的小型化。

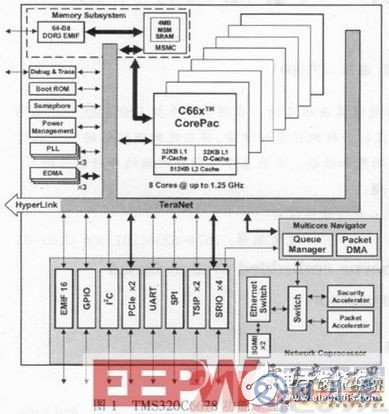

多核DSP是近年來針對高性能嵌入式應(yīng)用而出現(xiàn)的一類多核微處理器(MultiCore MicroProcessor)。相比傳統(tǒng)的單核處理器,多核處理器在提高并行處理能力的同時配置了更高的存儲帶寬和更靈活的存儲結(jié)構(gòu)。TMS320C6678是TI公司的最新型的KeyStone架構(gòu)多核DSP,該DSP集成了8個DSP內(nèi)核,每個內(nèi)核頻率可達1.25 GHz;定點運算能力為320 GMAC,浮點運算能力可達160 GFLOPS,運算能力比現(xiàn)在主流的DSP(如TS1 01)有大幅提高(TS101的內(nèi)核時鐘是300MHz,浮點運算能力為1 800 MFLOPS),充分體現(xiàn)并行處理的理念。每個DSP內(nèi)核配置32 kb的一級局部程序緩存器、32 kb的一級局部數(shù)據(jù)緩存器和512 kb的二級局部緩存器。TMS320C6678的功能原理圖如圖1所示。

基于KeyStone體系架構(gòu),能夠確保多核DSP的每一個內(nèi)核發(fā)揮全面的處理功能,TMS320C6678除了具有多DSP內(nèi)核導(dǎo)致的運算處理能力提高,還提供了豐富的對外通信接口以及存儲單元的支持,增強了處理器對外高速數(shù)據(jù)交換的吞吐能力。Keystone多核架構(gòu)為RISC和DSP內(nèi)核以及專用協(xié)處理器和I/O的集成提供了一種高性能的系統(tǒng)結(jié)構(gòu),Keystone架構(gòu)能夠在處理器內(nèi)核、外部設(shè)備、協(xié)處理器和I/O之間建立無阻塞數(shù)據(jù)傳輸,這主要基于多核導(dǎo)航器(MulTIcore Navigator)、TeraNet、多核共享存儲區(qū)控制器(MulTIcore Shared Memory Controller,)和超鏈接總線(HyperLink)。超鏈接總線和高速輸入輸出接口實現(xiàn)DSP與外界信息傳輸,TeraNet總線結(jié)構(gòu)(速度為2Tbps)把所有組成部分有機聯(lián)系在一起,包括作為主要處理單元的多個內(nèi)核以及通信協(xié)議處理器和數(shù)據(jù)信息包傳輸協(xié)處理器,能實現(xiàn)快速無沖突的內(nèi)部數(shù)據(jù)傳送。

多核共享存儲控制器(MSMC)配有DSP內(nèi)核共享的4 MBSRAM存儲器,對共享存儲器存取和信息包傳輸能夠并發(fā)進行;為了實現(xiàn)對外部存儲器快速存取,提供了速度為1 600 MHz的64位DDR3接口,尋址存儲空間可達到8 GB。多核導(dǎo)航器配置控制8192個多用途硬件隊列的隊列管理器,建立基于DMA的零開銷信息包傳送通道,當(dāng)需要并行處理的多任務(wù)被分配到隊列中,多核導(dǎo)航器通過將任務(wù)引導(dǎo)到適當(dāng)?shù)目捎糜布韺崿F(xiàn)任務(wù)的加速派遣。網(wǎng)絡(luò)協(xié)處理器支持信息包傳送加速和安全加速引擎,增強了與上位機的通信功能。TMS320C6678提供豐富的高速外設(shè)接口:四路串行高速IO(SRIO),每路傳輸速度最高可達到5 GBaud;兩通道PCIe—II傳輸,每通道速度最高可達5 GBaud;超鏈接總線(HyperLink)支持與其他具有KeyStone架構(gòu)的器件互連,傳輸速度可達到50 GBaud;16位擴展存儲器接口,支持256 MBNAND Flash和16 MB NOR Flash,支持異步SRAM容量可達到1 MB;以及16個GBIO接口等,諸多高速的外部接口可以保證多通道高采樣率的大量數(shù)據(jù)實時進入DSP內(nèi)核進行處理。另外,TM S320C6678具備動態(tài)電源監(jiān)測和SmartReflex電源管理技術(shù),能夠在低功耗和強大運算處理能力之間達到性能平衡。

綜上所述,TMS320C6678處理器為彈載高速實時大容量數(shù)據(jù)處理、數(shù)據(jù)傳輸和復(fù)雜算法實現(xiàn)提供了強大的硬件平臺基礎(chǔ)。其中的Keystone架構(gòu)提供了一種集成了片內(nèi)各種子系統(tǒng)的可編程平臺,該架構(gòu)使用多種開創(chuàng)性的技術(shù)和硬件組成使得芯片內(nèi)部和芯片之間的數(shù)據(jù)信息傳輸達到最佳化,從而保障各種DSP資源能夠高效無縫發(fā)揮作用。這種體系架構(gòu)的中樞是稱為多核導(dǎo)航器的關(guān)鍵組成單元,它能夠?qū)崿F(xiàn)各種芯片組成之間高效的數(shù)據(jù)管理,對各內(nèi)核進行管理和協(xié)調(diào),使得DSP內(nèi)核高效互聯(lián),保證多核處理器的效能得到發(fā)揮。Teranet交換網(wǎng)絡(luò)能實現(xiàn)2Tbps的無阻塞信息交換,能進行快速無沖突的內(nèi)部數(shù)據(jù)傳送,多核共享存儲控制器確保處理器內(nèi)核無需通過數(shù)據(jù)傳輸網(wǎng)絡(luò)就能夠直接存取共享存儲器和外部存儲器。

2 基于多核DSP的軟件設(shè)計

為了有效發(fā)揮多核DSP系統(tǒng)的運算處理和數(shù)據(jù)傳輸能力,獲得多核DSP實際應(yīng)用系統(tǒng)的最佳性能,需要進行相應(yīng)的基于多核DSP的系統(tǒng)軟件設(shè)計,軟硬件的有機配合,確保多核DSP的功能和性能真正發(fā)揮作用。對于基于多核DSP的信息處理系統(tǒng),盡管多核DSP提供了高性能硬件基礎(chǔ),在系統(tǒng)設(shè)計過程中,需要考慮每個內(nèi)核之間的任務(wù)分配和信息傳輸,因此,為充分利用多核DSP的硬件優(yōu)勢,多核DSP系統(tǒng)并行軟件設(shè)計是關(guān)鍵,多核DSP對軟件設(shè)計提出新的挑戰(zhàn),同時也導(dǎo)致軟件設(shè)計理念和設(shè)計方法的改變。

TMS320C6678集成了8個DSP內(nèi)核,多內(nèi)核之間的任務(wù)分配和系統(tǒng)處理算法直接影響多核系統(tǒng)的性能和效率。任務(wù)分配的目的就是合理配置系統(tǒng)資源,設(shè)法減少DSP內(nèi)核間的通訊開銷。均衡負載是將系統(tǒng)承擔(dān)的任務(wù)合理地分配給各DSP內(nèi)核,以提高系統(tǒng)吞吐量。顯然,減少通訊量和均衡負載是相互矛盾的,因此,系統(tǒng)任務(wù)分配策略也就是最大限度地減少各子系統(tǒng)間的通訊量,同時均衡各子系統(tǒng)問的負載,以提高整個系統(tǒng)的性能。

為了全面挖掘多核處理器的潛力、充分利用多核處理器的優(yōu)勢,軟件設(shè)計人員必須掌握相應(yīng)的并行軟件設(shè)計技術(shù),將彈載信息處理系統(tǒng)任務(wù)映射到各DSP內(nèi)核。任務(wù)并行是指軟件中的獨立任務(wù)同時執(zhí)行。對于一個單核處理器,各單獨任務(wù)必須共享同一個處理器;而在一個多核處理器上,各任務(wù)實質(zhì)上是相互獨立運行,從而導(dǎo)致更高效的任務(wù)執(zhí)行。

為了將彈載信息處理系統(tǒng)映射到多核處理器,需要識別任務(wù)的并行度并相應(yīng)選擇最適宜的處理模式。彈載多核DSP系統(tǒng)的并行處理模式可采用數(shù)據(jù)流模式。數(shù)據(jù)流模式表現(xiàn)為分布式控制和執(zhí)行,處理任務(wù)依次通過如同流水線一樣的各處理階段。每個內(nèi)核使用各種算法處理一組數(shù)據(jù),然后這些數(shù)據(jù)被傳送到另一個內(nèi)核做進一步處理。初始內(nèi)核通常與一個輸入接口相連接,通過該接口可接收來自A/D轉(zhuǎn)換器或FPGA的待處理的初始數(shù)據(jù)。調(diào)度的觸發(fā)依賴于數(shù)據(jù)的可用性。由于彈載信息處理系統(tǒng)包含大量復(fù)雜的運算成分和信號與信息處理算法,它們互相關(guān)聯(lián)且不可能在一個內(nèi)核上處理完成。采用該模型需要將復(fù)雜的處理任務(wù)劃分到各內(nèi)核并確保系統(tǒng)具有高數(shù)據(jù)流動速率。系統(tǒng)的組成通常需要被拆分并映射到多個內(nèi)核中,并確保處理數(shù)據(jù)有規(guī)則地流水傳送。高速數(shù)據(jù)傳輸速率要求各內(nèi)核之間具備適宜的存儲帶寬,各內(nèi)核之間數(shù)據(jù)流動是規(guī)則的,并確保數(shù)據(jù)傳送開銷低。數(shù)據(jù)流處理模型如圖2所示。該處理模型要求每個處理器內(nèi)核映射一個或多個任務(wù),而各內(nèi)核之間通過消息傳遞實現(xiàn)運行同步;各內(nèi)核之間的數(shù)據(jù)傳送通過共享存儲器或DMA方式進行。

對于多核信息處理系統(tǒng),完成并行任務(wù)的辯識后,任務(wù)的映射和調(diào)度也需要精心策劃。多核并行處理系統(tǒng)軟件設(shè)計可以遵循四步處理法原則,即發(fā)現(xiàn)并行執(zhí)行的機會,其核心是定義大量的小型任務(wù),以便得到待解決問題的高效分解;定義任務(wù)之間的信息流動和數(shù)據(jù)傳輸;確定在多核架構(gòu)上高效運行的任務(wù)組;以及將各任務(wù)映射分配到各內(nèi)核中,確定每個任務(wù)將由哪個內(nèi)核執(zhí)行。為了提高多核系統(tǒng)軟件開發(fā)效能,開展基于嵌入式實時操作系統(tǒng)的軟件開發(fā),在操作系統(tǒng)和多核軟件開發(fā)工具支持下,自動識別任務(wù)的并行性并將各處理任務(wù)映射到單個內(nèi)核,為多個實時任務(wù)合理分配資源,有效實現(xiàn)系統(tǒng)進程管理,方便多任務(wù)程序?qū)崟r調(diào)度,確保多核DSP能夠發(fā)揮最佳系統(tǒng)性能。

3 結(jié)束語

隨著DSP技術(shù)的不斷發(fā)展和應(yīng)用需求的不斷提高,單片多核處理器結(jié)構(gòu)逐漸成為DSP發(fā)展的主流,單片多核處理器具有強大的多任務(wù)實時運算處理能力,同時具備數(shù)據(jù)搬移、通訊、資源共享和存儲器管理等有利于并行任務(wù)執(zhí)行的豐富硬件配置,能很好地支持多任務(wù)實時并行處理。對于小尺寸、低功耗且運算處理性能要求極高的彈載信息處理系統(tǒng),多核DSP使得彈載雷達信息處理能夠?qū)崟r實現(xiàn)目標探測識別以及目標信息高分辨測量等復(fù)雜系統(tǒng)算法,能夠帶來性能/功耗比的大幅提升。采用多核DSP也成為彈載雷達信息處理系統(tǒng)的發(fā)展趨勢。對于多核DSP應(yīng)用系統(tǒng),軟件設(shè)計是多核DSP性能能否充分發(fā)揮的系統(tǒng)設(shè)計關(guān)鍵。對于基于多核DSP的彈載信息處理系統(tǒng),運用數(shù)據(jù)流處理模式將系統(tǒng)處理任務(wù)劃分映射到各處理器內(nèi)核以實現(xiàn)高效實時并行處理。在嵌入式實時操作系統(tǒng)和多核軟件開發(fā)工具支持下,開展基于多核DSP并行軟件開發(fā)將成為彈載信息處理系統(tǒng)軟件設(shè)計的新課題。